Grouping

- Pipeline grouping[1]is a must for high functionality, low cost. For example it is used for memory access from 1 coordinate and parallelly transforming coordinate and then operating on the result of both.

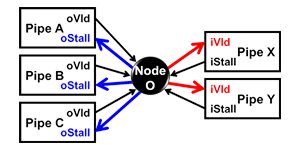

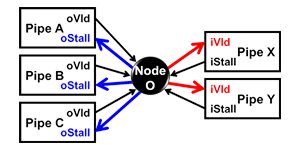

- For Node 0, using oVld, iStall of end stage of each pipeline, new iVld�ired color in below diagram�j, oStall�iBlue in below diagram�j are generated.

- For Node 0, required sufficient condition�iNASC�j is as following equation. Node is assumed to be module so be careful of prefix being reversed.�iFor example, oVld of Pipe A is iVld of Node 0�j

| NASCO = |

N-1

��

i=0 |

iVldi |

M-1

��

i=0 |

oStalli |

Here N and M are eachgrouping of front stage and back stage[2] |

Simple grouping method sample RTL

| Simple grouping method |

- Required sufficient condition�iNASC�j is true then, assert all oVld after grouping, and de-assert all iStall before grouping

- iStalliby itself relates to iVldi, hence if for previous stage any type other thanBuffer Type�iS�U�j is used, iVldiwill bedeasserted foreverand will not function

- oVldiby itself relates to oStalli, hence if for following stage if for throughput controlInput control type is used,looped combination circuit[3]occurs

|

module node(iVld, iStall, oVld, oStall);

parameter N = 4;

parameter M = 4;

input [N-1:0] iVld;

output [N-1:0] iStall;

output [M-1:0] oVld;

input [M-1:0] oStall;

wire nasc = (&iVld) & (~|oStall);

assign iStall = {N{~nasc}};

assign oVld = {M{nasc}};

endmodule

|

General grouping method sample RTL

| General grouping method |

- Required sufficient condition�iNASC�jis true then, oVld after grouping is asserted with below condition, and iStall before grouping is dasserted with below conditions.

- iStalliby itself is excludes relation to iVldi

- oVldiby itself excludes relation to oStalli

- With the below condition also, if for throughput control to later stagesInput control typearemultipleused, then looped combined circuit[3]will occur

|

module node(iVld, iStall, oVld, oStall);

parameter P = 2;

parameter Q = 2;

parameter M = 1<<P;

parameter N = 1<<Q

input [N-1:0] iVld;

output [N-1:0] iStall;

output [M-1:0] oVld;

input [M-1:0] oStall;

reg [N-1:0] iStall;

reg [M-1:0] oVld;

integer i;

always @(iVld or oStall)

for (i=0; i<N; i=i+1)

iStall = ~&vldSerFunc(iVld, i) | (|oStall);

always @(iVld or oStall)

for (i=0; i<M; i=i+1)

oVld = &iVld & (~|StallSerFunc(oStall, i));

function [N-1:0] vldSerFunc;

input [N-1:0] vld;

input [Q-1:0] num;

integer i;

for (i=0; i<N; i=i+1)

vldSerFunc[i] = (i == num) ? 1'b1 : vld[i];

endfunction

function [M-1:0] StallSerFunc;

input [M-1:0] Stall;

input [P-1:0] num;

integer i;

for (i=0; i<M; i=i+1)

StallSerFunc[i] = (i == num) ? 1'b0 : Stall[i];

endfunction

endmodule

|

Logical design circuit > Pipeline > Grouping Next Page�iThroughput control�j Top of this page ��