目的

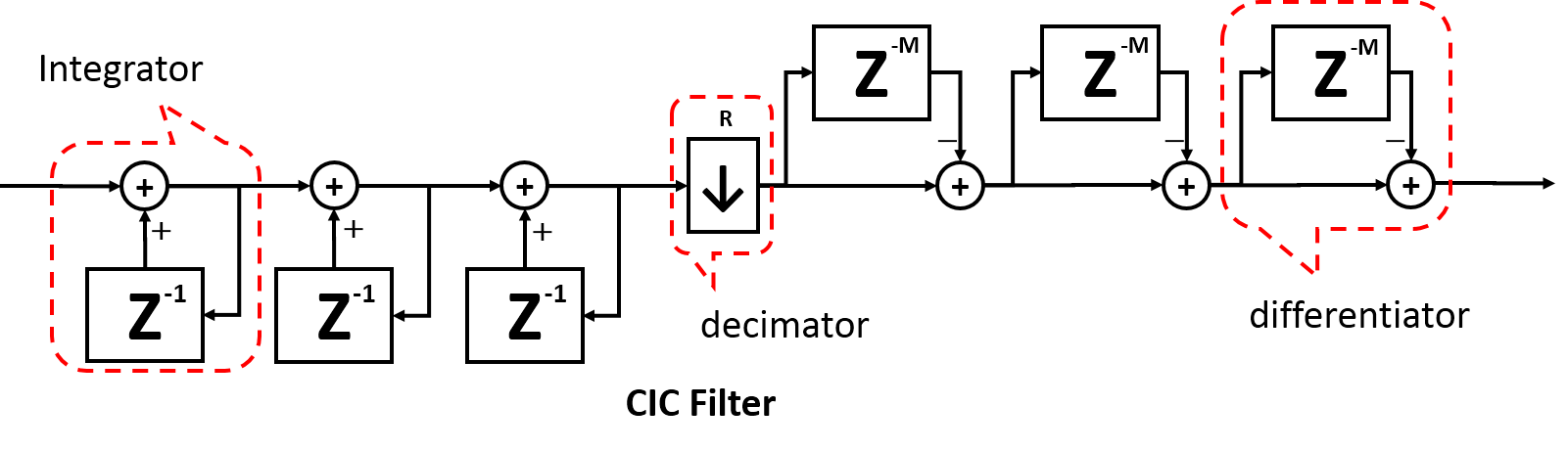

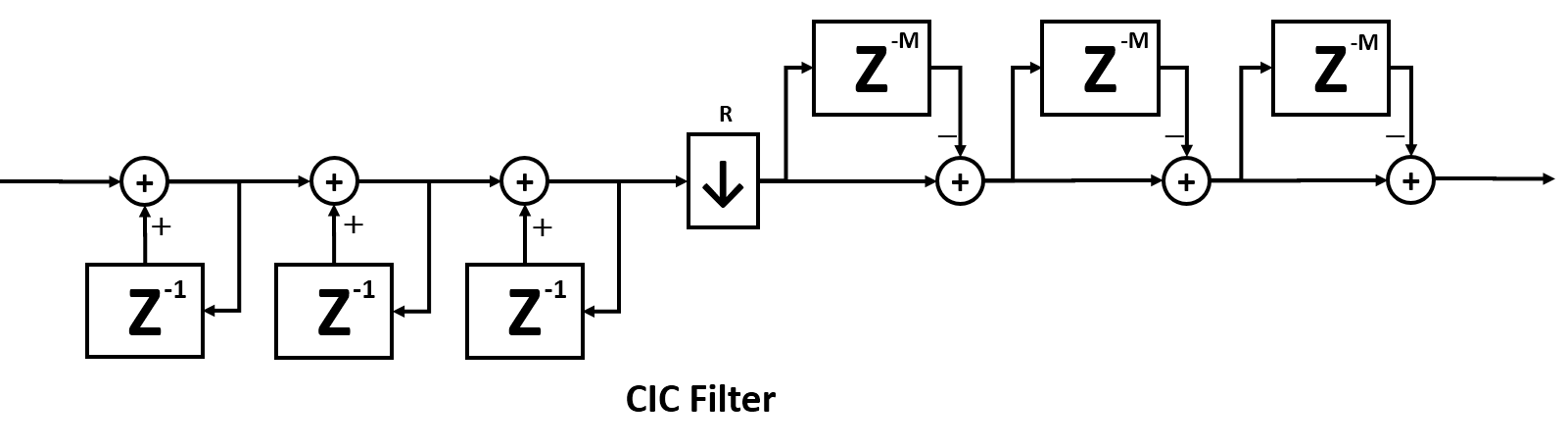

- サンプリング周波数変換などに使用されるCICフィルタは以下のように積分器をカスケードしたものと微分器をカスケードしたものをデシメータで接続したものです。周波数変換時のエイリアスを防ぐため積分器や微分器などで構成されたフィルタと周波数変換を行うデシメータで構成されます。

- 使用用途に合わせたフィルタ構成とするためにはタップ数(N)やデシメーションの変換率(R)などを調整することが必要です。またCICフィルタによるビット幅の増殖分も考慮する必要があります。毎回使用用途に合わせてCICフィルタの実装を行わなくて済むように、これらの値をパラメータ化した論理設計を目指します[1]。

- CICフィルタではタップ数Nを大きくすることで減衰率を大きくすることが出来ます。減衰率が上がるとホワイトノイズがのらないような入力データのビット幅が必要となってきます。

ビット幅が増えてくると加算処理のCarry伝播による速度の問題が懸念されます。そこで、Carryの伝播を抑えるCarry Save Adder(CSA)を使用した加算処理の高速化[2]についても触れることにします。

[テスト・考察]にてCSAに関する考察を掲載しました。またCSAについてはテクニック[高速演算]をご確認ください。

CICフィルタとは[3][4]

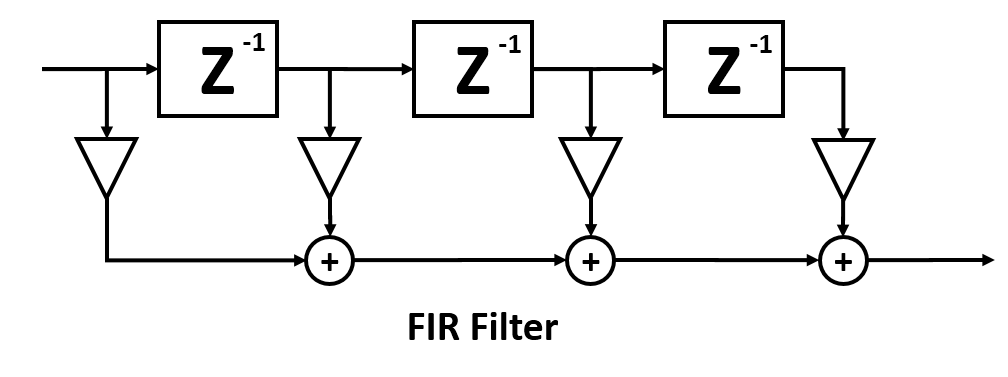

- サンプリング周波数のレート変換などでフィルタリングを行う必要がある場合FIRフィルタなどのデジタルフィルタを用いることができます。しかしながらFIRフィルタは乗算処理で構築されており多くのタップ数が必要となる場合には回路規模が大きくなるという問題があります。また通信などの高速な処理が必要となる場合に処理速度が問題となってきます。

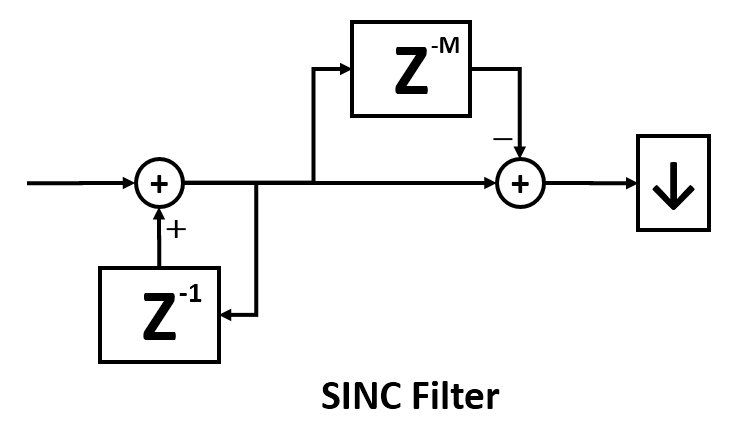

- このような場合にはFIRフィルタより性能が落ちますが乗算器を必要とせず加算器だけを使用しているSINCフィルタを使用することができます。

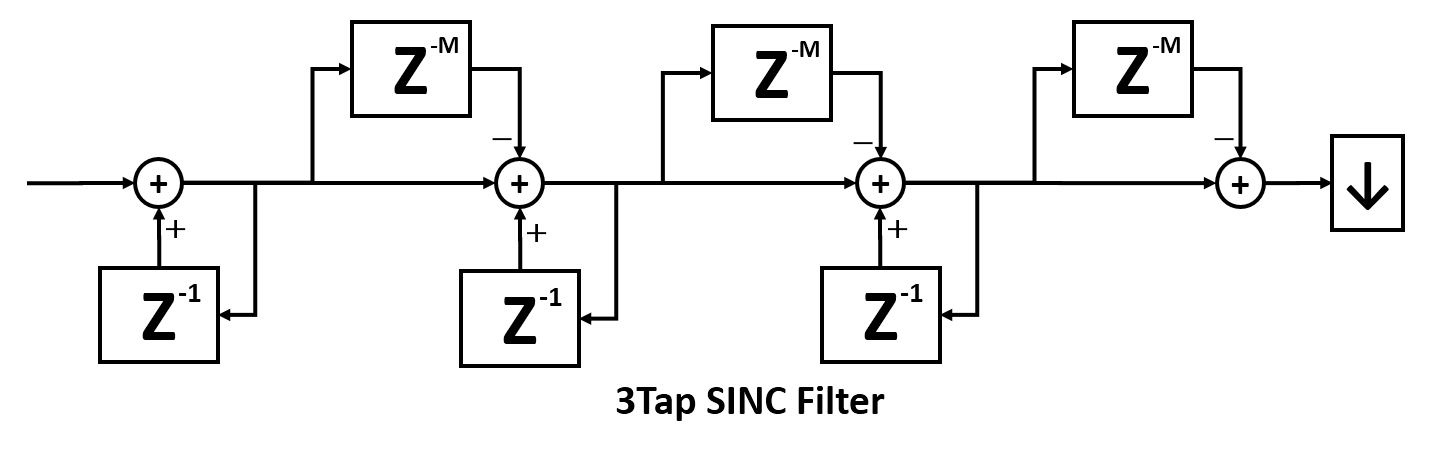

- SINCフィルタは複数のタップ数で使用されることが多く、以下のようにSINCフィルタをカスケードして使用します。これらの積分器と微分器の位置を変えて集めたものをCICフィルタと呼びます。

- このような構成にすることで加算処理だけでの構成に出来ることのメリットだけではなく、デシメータは積分器と微分器のクロック比率を調整することで実現できるようになります。微分器はデシメートされた分だけのデータを処理すれば良い事になり微分器にある遅延素子を減らすこともできます。これらは実装面や速度面での大きなメリットが得られることになります。CICフィルタの設計を行うにあたりタップ数などのパラメータの決め方は「CIC Filter Introduction」などをご参照ください。[3]

回路デザイン > 設計例 [CICフィルタ] > 目的・考え方 次のページ(実装にあたって) このページのTOP ▲