コーディング

- タップ数はトップモジュールのTAP_NUMにより指定します。本パラメータが積分モジュール、微分モジュールに引き渡されることで各モジュールのタップ数が変更されます。

- 微分モジュールの遅延数はトップモジュールのDELAY_NUMにより指定します。本パラメータが微分モジュールに引き渡されることで遅延量が変更されます。

- デシメーション変換率は積分器のクロックと微分器のクロックの比率で指定します。このクロックは外部で生成してCICフィルターに入力することでデシメーションを実現します。

- 演算結果を任意のタイミングでリセットすることが出来るようにリセットは同期リセットにしています。

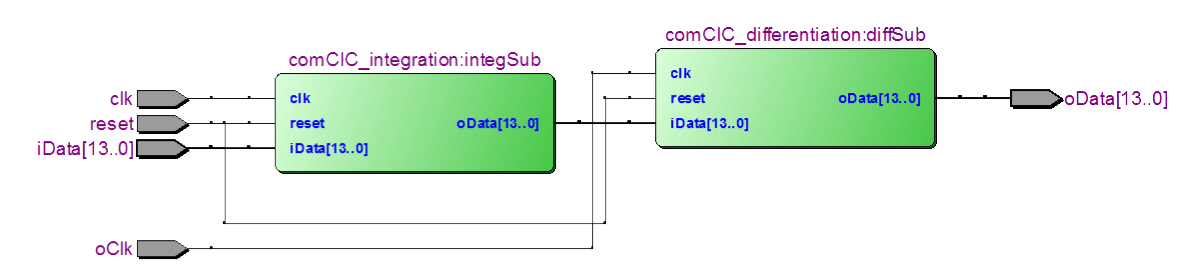

トップモジュール

/* **************************** MODULE PREAMBLE ********************************

Copyright (c) 2012, ArchiTek

This document constitutes confidential and proprietary information

of ArchiTek. All rights reserved.

*/

// ***************************** MODULE HEADER *********************************

// -----------------------------------------------------------------

// CICフィルタモジュール

// 積分フィルタ+デシメーション+微分フィルタ+デシメーションを行う

// 以下パラメータにて構成を変更する

// -----------------------------------------------------------------

module comCIC(

iData,

oData,

clk,

oClk,

reset

);

// ************************ PARAMETER DECLARATIONS *****************************

// -----------------------------------------------------------------

// パラメータは下位モジュールに引き渡す

// パラメータの整合性チェックは行われないので間違いのないように

// 上位より指定する必要がある

// -----------------------------------------------------------------

// -----------------------------------------------------------------

// カスケードした積分・微分フィルタのタップ数を指定

// -----------------------------------------------------------------

parameter TAP_NUM = 3;

// -----------------------------------------------------------------

// 微分フィルタの遅延数を指定

// 通常 1か2

// -----------------------------------------------------------------

parameter DELAY_NUM = 1;

// -----------------------------------------------------------------

// CICフィルタ内部でのデータビット幅を指定

// ビット幅の計算は以下に従って計算します

// BIT_W = Data bit + TAP_NUM * log2(RE_SAMP * DELAY_NUM)

// 入力データのビットが8ビット

// TAP数が3 (TAP_NUM=3)

// 積分・微分フィルタの間にあるデシメーション 1/4

// なお、RE_SAMPの本moduleへの指定は clkとoClkの周波数比に

// よって行う

// 今回上位モジュールでoClkをclkの1/4にしている

// 微分フィルタ遅延数が1(DELAY_NUM=1)

// BIT_W = 8 + 3 * log2(4 * 1)

// = 8 + 3 * 2 = 8 + 6 = 14

// -----------------------------------------------------------------

parameter BIT_W = 14;

// ***************************** I/O DECLARATIONS ******************************

input [BIT_W-1:0] iData; // 入力データ

output [BIT_W-1:0] oData; // 出力データ

input clk; // クロック

input oClk; // デシメーション用クロック

input reset; // リセット

// **************************** LOCAL DECLARATIONS *****************************

wire [BIT_W-1:0] integDat; // 積分フィルタ→微分フィルタ

wire [BIT_W-1:0] diffDat; // 微分フィルタ→デシメーション

// ****************************** MODULE BODY **********************************

// ---------- Integration Block ------------

// -----------------------------------------------------------------

// 積分フィルタブロック

// 本ブロックの内部でタップ数分カスケードする

// -----------------------------------------------------------------

comCIC_integration

#(TAP_NUM, BIT_W)

integSub(

.iData (iData),

.oData (integDat),

.clk (clk),

.reset (reset)

);

// ---------- Differentiation Block ------------

// -----------------------------------------------------------------

// 微分フィルタブロック

// 本ブロックの内部でタップ数分カスケードしている

// またクロックをoClkを入れることでデシメーションする

// -----------------------------------------------------------------

comCIC_differentiation

#(TAP_NUM, DELAY_NUM, BIT_W)

diffSub(

.iData (integDat),

.oData (diffDat),

.clk (oClk),

.reset (reset)

);

assign oData = diffDat;

endmodule

// *****************************************************************************

トップモジュール図

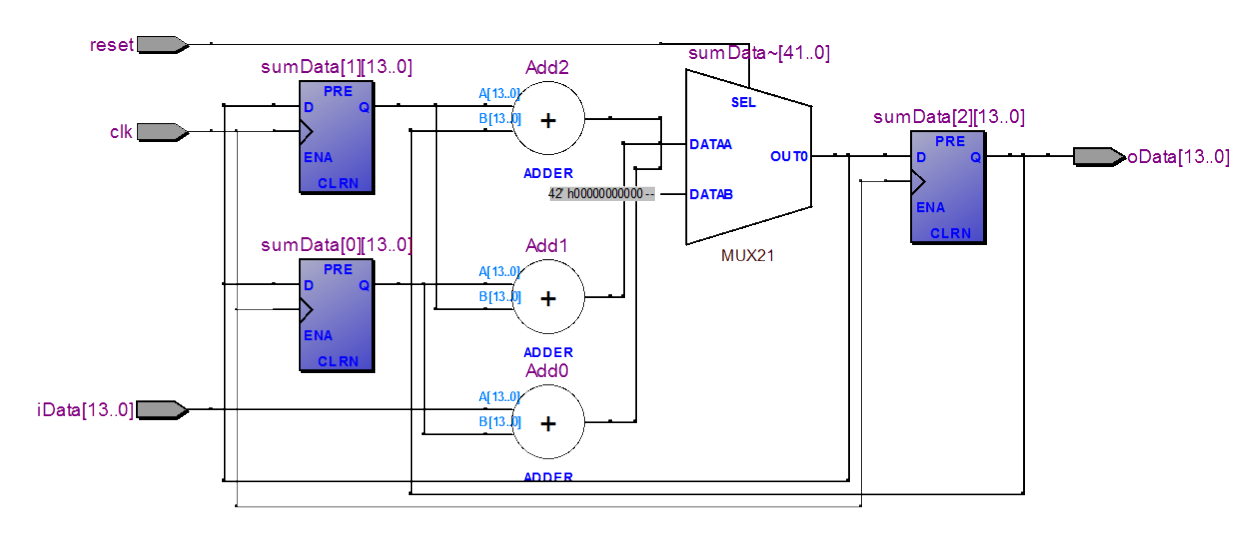

積分モジュール

/* **************************** MODULE PREAMBLE ********************************

Copyright (c) 2011, ArchiTek

This document constitutes confidential and proprietary information

of ArchiTek. All rights reserved.

*/

// ***************************** MODULE HEADER *********************************

// -----------------------------------------------------------------

// 積分フィルタモジュール

// パラメータのTAP_NUMでカスケードする数を指定される

// -----------------------------------------------------------------

module comCIC_integration(

iData,

oData,

clk,

reset

);

// ************************ PARAMETER DECLARATIONS *****************************

parameter TAP_NUM = 3;

parameter BIT_W = 14;

// ***************************** I/O DECLARATIONS ******************************

input [BIT_W-1:0] iData;

output [BIT_W-1:0] oData;

input clk;

input reset;

// **************************** LOCAL DECLARATIONS *****************************

// -----------------------------------------------------------------

// 積分フィルタのタップから出力された結果を保持する

// 次データ処理時に前回結果として利用している

// -----------------------------------------------------------------

reg [BIT_W-1:0] sumData[0:TAP_NUM-1];

// -----------------------------------------------------------------

// タップ数をfor文で記述するためのカウンタ

// -----------------------------------------------------------------

integer i;

// ****************************** MODULE BODY **********************************

// -------------------------------------------------

// 入力データとひとつ前の結果との加算処理

// -------------------------------------------------

always @(posedge clk)

if(reset)

// -------------------------------------------------

// リセット時の初期化

// -------------------------------------------------

for(i=0 ; i < TAP_NUM ; i=i+1)

sumData[i] <= #1 {BIT_W{1'b0}};

else begin

// -------------------------------------------------

// 一つ目は入力データと前回の結果を加算

// -------------------------------------------------

sumData[0] <= iData + sumData[0];

// -------------------------------------------------

// 二つ目移行は前のタップの結果と前回の結果を加算

// -------------------------------------------------

for(i=1 ; i < TAP_NUM ; i=i+1)

sumData[i] <= #1 sumData[i-1] + sumData[i];

end

// -------------------------------------------------

// 最後タップの結果を出力

// -------------------------------------------------

assign oData = sumData[TAP_NUM-1];

endmodule

// *****************************************************************************

積分モジュール図

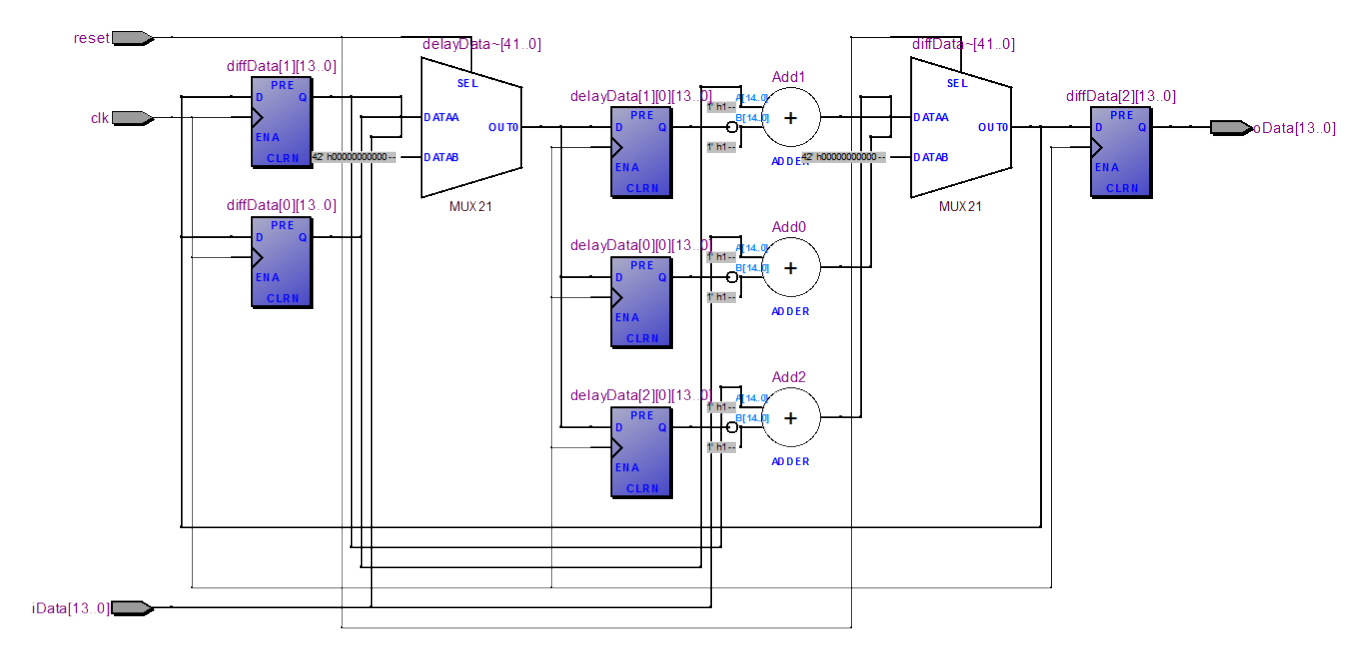

微分モジュール

/* **************************** MODULE PREAMBLE ********************************

Copyright (c) 2011, ArchiTek

This document constitutes confidential and proprietary information

of ArchiTek. All rights reserved.

*/

// ***************************** MODULE HEADER *********************************

// -----------------------------------------------------------------

// 微分フィルタモジュール

// パラメータのTAP_NUMでカスケードする数を指定される

// -----------------------------------------------------------------

module comCIC_differentiation(

iData,

oData,

clk,

reset

);

// ************************ PARAMETER DECLARATIONS *****************************

parameter TAP_NUM = 3;

parameter DELAY_NUM = 1;

parameter BIT_W = 14;

// ***************************** I/O DECLARATIONS ******************************

input [BIT_W-1:0] iData;

output [BIT_W-1:0] oData;

input clk;

input reset;

// **************************** LOCAL DECLARATIONS *****************************

// -----------------------------------------------------------------

// 微分フィルタのタップから出力された結果を保持する

// 次データ処理時に前回結果として利用される

// -----------------------------------------------------------------

reg [BIT_W-1:0] diffData[0:TAP_NUM-1];

// -----------------------------------------------------------------

// 遅延するためデータを保持する

// タップ数と遅延分の2次元配列となる

// -----------------------------------------------------------------

reg [BIT_W-1:0] delayData[0:TAP_NUM-1][0:DELAY_NUM-1];

// -----------------------------------------------------------------

// タップ数をfor文で記述するためのカウンタ

// -----------------------------------------------------------------

integer i;

// -----------------------------------------------------------------

// 遅延データをfor文で記述するためのカウンタ

// -----------------------------------------------------------------

integer j;

// ****************************** MODULE BODY **********************************

// -------------------------------------------------

// 遅延処理処理

// -------------------------------------------------

// --------- Delay ---------

always @(posedge clk or negedge reset_n)

if(reset)

// -------------------------------------------------

// リセット時の遅延データ初期化

// -------------------------------------------------

for(i=0 ; i < TAP_NUM ; i=i+1)

for(j=0 ; j < DELAY_NUM ; j=j+1)

delayData[i][j] <= #1 {BIT_W{1'b0}};

else begin

// -------------------------------------------------

// 遅延データの格納

// -------------------------------------------------

for(i=0 ; i < TAP_NUM ; i=i+1) begin

if(i == 0)

// -----------------------------------------

// 一つ目のタップの入力は入力データ

// -----------------------------------------

delayData[i][0] <= #1 iData;

else

// -----------------------------------------

// 二つ目以降のタップの入力は前のタップの結果

// -----------------------------------------

delayData[i][0] <= #1 diffData[i-1];

// -----------------------------------------

// 遅延分ループ

// -----------------------------------------

for(j=1 ; j < DELAY_NUM ; j=j+1)

delayData[i][j] <= #1 delayData[i][j-1];

end

end

// -------------------------------------------------

// 入力データとひとつ前の結果との減算処理

// -------------------------------------------------

// --------- Diff ---------

always @(posedge clk or negedge reset_n)

if(reset)

// -------------------------------------------------

// リセット時の結果データ初期化

// -------------------------------------------------

for(i=0 ; i < TAP_NUM ; i=i+1)

diffData[i] <= #1 {BIT_W{1'b0}};

else begin

// -------------------------------------------------

// 一つ目は入力データと前回の結果を減算

// -------------------------------------------------

diffData[0] <= #1 iData - delayData[0][DELAY_NUM-1];

// -------------------------------------------------

// 二つ目移行は前のタップの結果と遅延させたものを減算

// -------------------------------------------------

for(i=1 ; i < TAP_NUM ; i=i+1)

diffData[i] <= #1 diffData[i-1]

- delayData[i][DELAY_NUM-1];

end

// -------------------------------------------------

// 最後タップの結果を出力

// -------------------------------------------------

assign oData = diffData[TAP_NUM-1];

endmodule

// *****************************************************************************

微分モジュール図

回路デザイン > 設計例 [CICフィルタ] > コーディング 次のページ(テスト・考察) このページのTOP ▲