目的

- 設計例 [DDR制御(論理)]で記述した内容をベースに、実動作にてその機能確認を行うために実機へのインプリメントを行います。今回はXilinx社製Virtex-6 FPGA ML605評価キットを使用します。

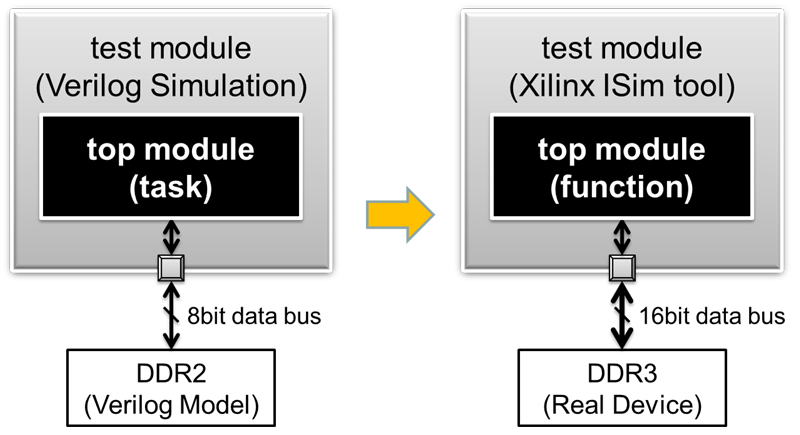

- 基本的にほとんどのVerilogソースコードが流用可能ですが、Verilogシミュレータのテストベンチ対応の記述は実機では無効となるので削除します。またDDR制御(論理)ではシミュレーション用にtsc[31:0]という時間変数を使用してタスク処理していましたが、実機の場合は電源投入直後からクロックに同期して動作するので、今回は電源投入後自動的にメモリのライト/リードアクセステストを行うようにします。実行状態はプログラムカウンタ(pcという変数)で管理し、ファンクションで処理します。

- DDR制御(論理)ではメモリデバイスがDDR2 8bitデータバスを対象にしていましたが、本実装編ではVirtex-6 FPGA ML605評価キットに搭載されているメモリデバイスがDDR3 16bitデータバスですのでその変更対応も行います。テストベンチファイルは残りますがXilinxのISimツール検証用で、実動作には使用しません。概要をまとめると以下のイメージ図のようになります。

- DDR2とDDR3については、速度、機能制限、端子の別活用などの差で、基本的に統一した設計思想で対応できます。詳細はDDR制御(論理)の内容を参照して下さい。ここでは実装を行う上でのポイントを中心に記述していきます。

考え方(DDR Dataパス)

- 通常の実機システムではDDRメモリは複数個のモジュールとして搭載されていますので、メモリコントローラでは複数のデバイスに対してタイミング特性を満たしながらアクセスを行う必要があります。

- DDR3ではデバイスに入力されるクロック周波数が400〜666MHzと高速になりますので、DIMM(Dual Inline Memory Module)のような複数のデバイスに対してクロックスキューを調整しながらアクセスする際はFly-byトポロジー[1]を採用してタイミング調整を行っています。

- このような複数のDDRデバイスを制御するメモリコントローラのI/Fには専用のPHY(DDRに直接インターフェイスする部分。DDR制御(論理)編 実装にあたっての[全体像]を参照のこと)を設計する必要があります。独自で設計することは非常に困難なので、FPGAを供給するメーカーではDDR用の専用IPコアを提供しています。Xilinx社の場合もMIG(Memory Interface Generator)[2]と呼ばれるDDR2/DDR3用のIPコアを準備しているので、それを使用するのが一般的です。

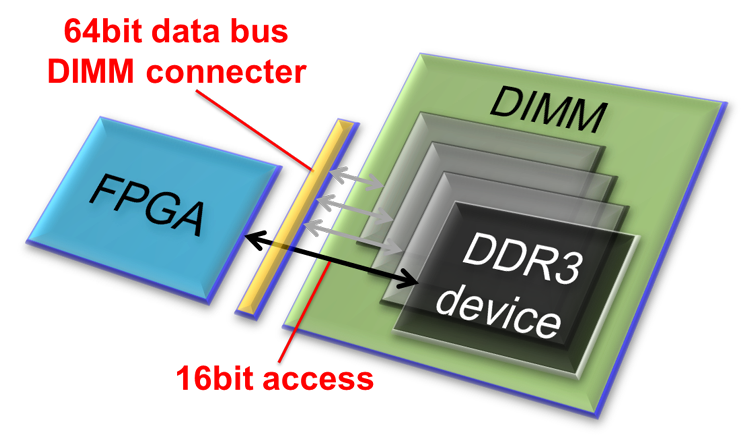

- しかしながら今回は、DDR制御(論理)編で単一のデバイスに対してメモリアクセスするコントローラを設計しましたので、それを実機にインプリメントすることにします。したがってまず最初にあくまでも論理検証用の独自システムであることを認識しておいて下さい。

- 今回使用するXilinx社製Virtex-6 FPGA ML605評価キットではDDRメモリとしてMicron社製のSODIMM(MT4JSF6464HY-1G1)を搭載しています。このDIMMには8Meg×16×8banksの1Gbit DDR3デバイスが4個実装されています。今回はこの「DDR3 16bit Busデバイス1個」に対してのみアクセスする検証システムとなります。

- FPGAとDDR3デバイスの接続はVirtex-6 FPGA ML605評価キットの端子配置に準じます。詳細はML605ハードウェアユーザーガイドの詳細説明「2. 512MB DDR3メモリ SODIMM」を参照して下さい。DDR3データバスはDDR3_D0〜D15を使用します。

考え方(クロック供給)

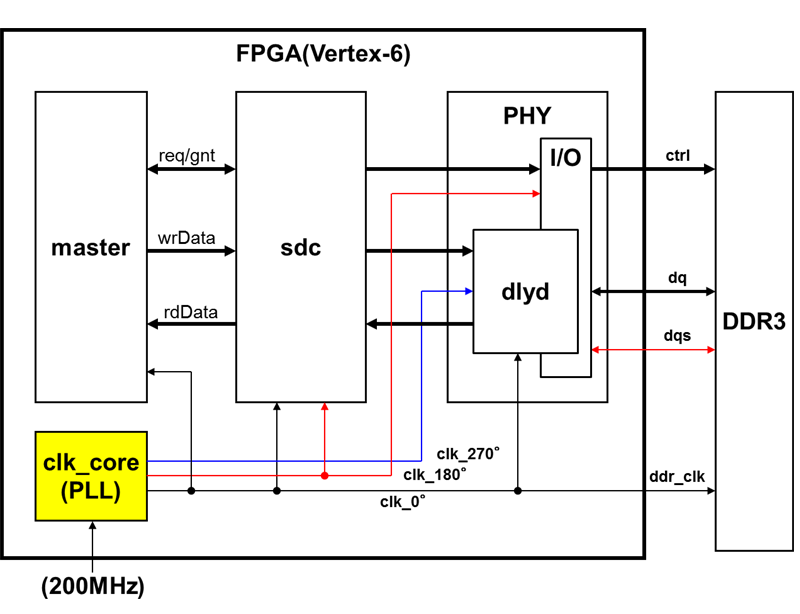

- 実装システムのクロック供給について考えます。DDR制御(論理)編では制御に使用する単一クロックに対して、0°、90°、180°、270°位相をずらしたクロックを最上位モジュールで生成していました(実際は+90°クロックは内部では未使用)。今回はFPGA内部でPLLを使用してこれらのクロックを作成します。Xilinx社の設計ツールで"Core Generator"を使用してクロックのIPコアを作成します。

- FPGA内部での実際のクロック接続系統図概要は以下のようになります。内部の基本動作はclk0°同期、DDR制御信号(アドレス、ras、cas、we等)はclk0°でサンプリングするためclk180°同期、DDRライトデータ信号はDDRクロック両エッジでサンプリングするためclk270°同期となります。

- FPGA内部のPLLコアに入力されるクロックはML605評価キットの200MHzを使用します。PLLの出力周波数はIPコア生成の際にパラメータとして設定します。これによりデバッグの過程でクロック周波数を可変にして動作検証を行うことができます。各位相クロックの周波数値は当然同一ですが、今回はDDR制御(論理)編で記述した通りFPGA内部の動作周波数と外部DDRの動作周波数が同期しているシステムなので、通常DDR3はクロック周波数を400MHz以上で動作させますが、FPGA内部回路の動作速度を考慮して入力周波数と同じ200MHz程度までを動作目標とします[3]。

- 動作周波数が200MHzでは、DDR3デバイス最低動作周波数のスペック外にあたる可能性がありますが、先にも述べたように本構成はあくまでも論理検証用の独自システムですのでその点は御了承下さい。

回路デザイン > 設計例 [DDR制御(実装)] > 目的・考え方 次のページ(実装にあたって) このページのTOP ▲