タイミング調整の考え方

- DDRアクセスにおいてコントローラ側でデータと制御信号を作成してメモリとI/Fする場合、ライトサイクルにおいてはFPGA内部クロックに同期した信号を出力すれば良いので制御が容易で高速動作も可能になります。

- しかしながらリードサイクルにおいては、メモリが出力するクロック(DQS)とデータに対してうまくデータを取り込み、FPGA内部クロックに同期合わせをし直して処理を行う必要があります。

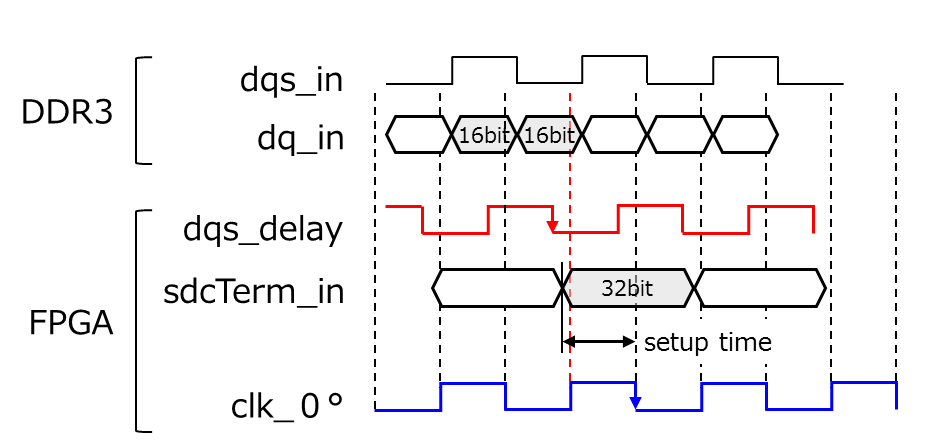

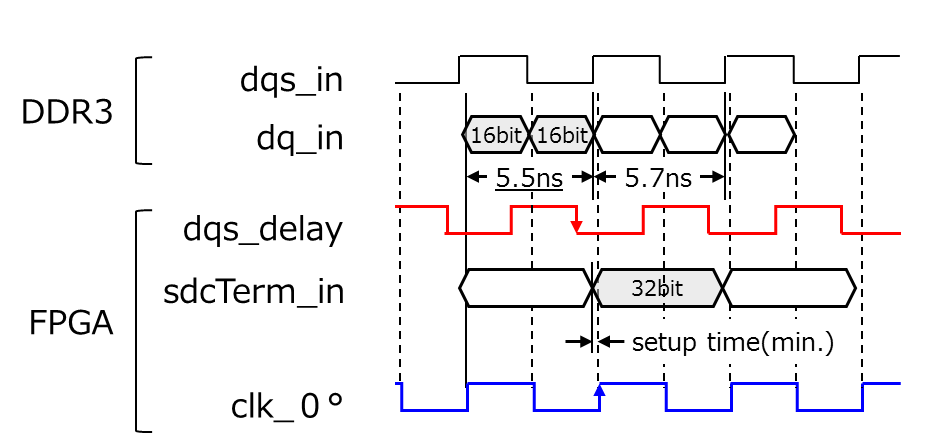

- 実装にあたっての中で説明した通り、今回のように内部クロックと外部クロックが同じ周波数でもDDR3から入ってくるクロックの位相差によってデータが取り込めなくなる可能性があります。例えば下記に示すタイミングであれば立ち上がりクロックに対するセットアップタイムが十分でないので、立下りクロックでサンプリングする方が確実です。

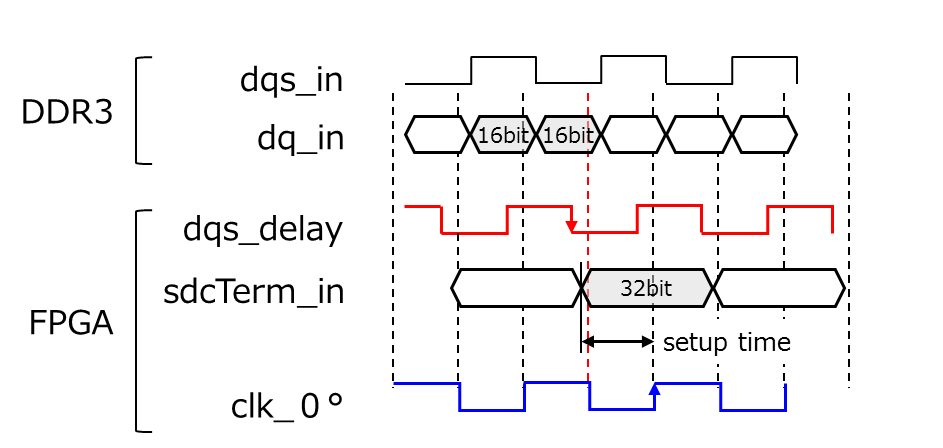

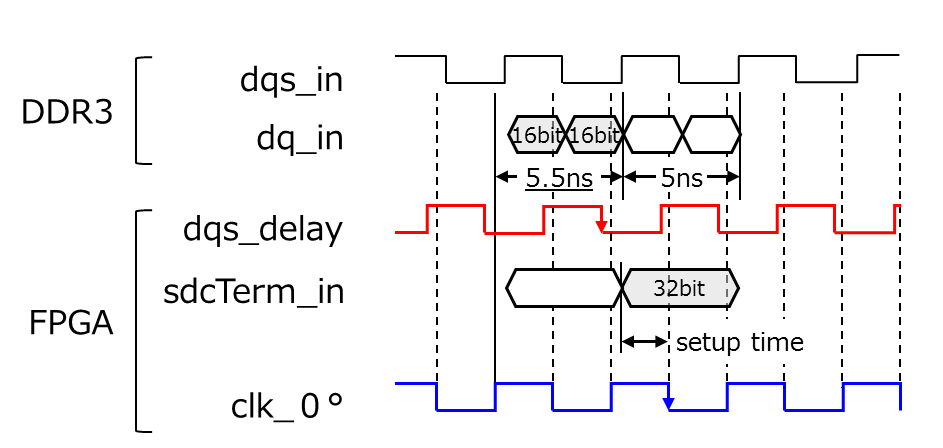

- それに対して、もし下記に示すタイミングであれば立下りクロックに対するセットアップタイムが十分でないので、立ち上がりクロックでサンプリングする方が確実です。

- 動作周波数が高速になれば上記条件はより厳しくなります。またDIMMのようにデータが多bitになった場合は、各bitに対して微調整が必要になります。メーカーが準備するDDR用の専用IPコアも機能としては各データbitの取り込みタイミングを監視して、セットアップタイムが十分となるようにマイコン[1]でサンプリングするF/Fのクロックエッジを切り替えることを行っています。今回はこの切り替えを手動で実施してタイミング調整を行い、動作周波数の高速化と最適化を行います。

今回の調整結果1

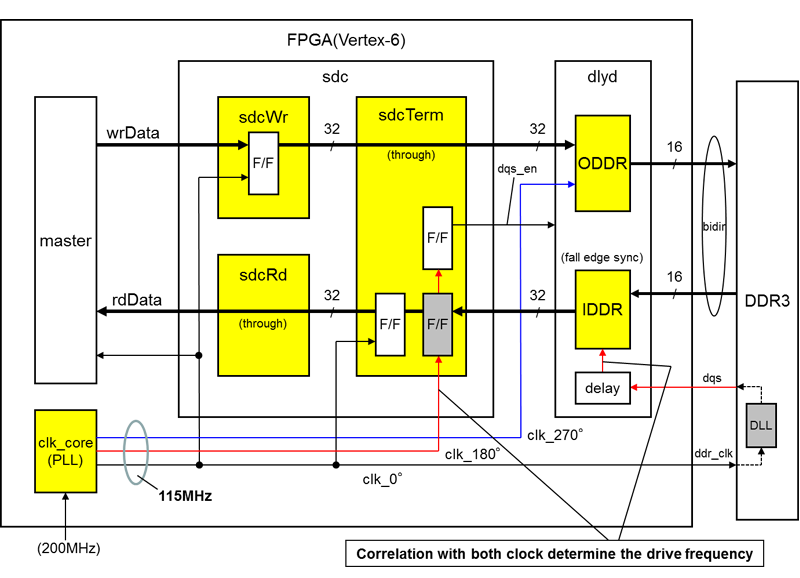

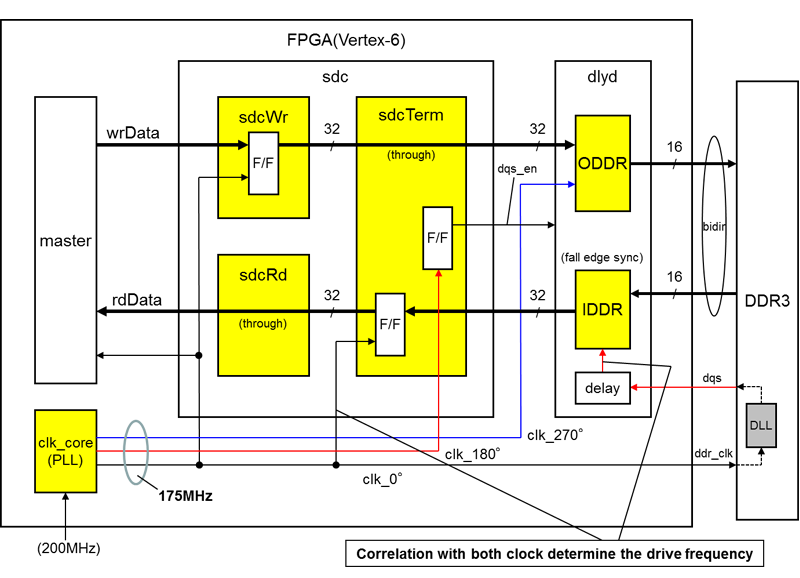

- この図は、FPGAからDDR3に接続されるライト/リードそれぞれのデータパスとクロックの関係を表しています。リードデータはsdcTermの中でclk_180°でサンプリングした後、clk_0°でサンプリングして内部クロックと同期します。この状態で内部の動作限界周波数を見極めた結果、正常動作する上限周波数は115MHzでした。

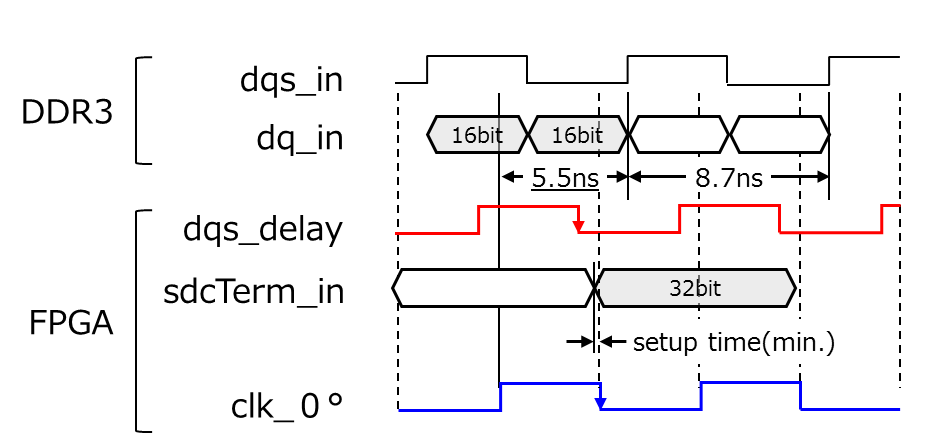

- 上記結果より、内部の取り込みタイミングの時間関係はおよそ以下のようになっていると考えられます。

今回の調整結果2

- この図は、FPGAからDDR3に接続されるライト/リードそれぞれのデータパスとクロックの関係で、調整結果1に対してsdcTerm中でのclk_180°サンプリングを削除してclk_0°のみでサンプリングしたものです。したがってリードデータはすぐに内部クロックと同期します。この状態で内部の動作限界周波数を見極めた結果、正常動作する上限周波数は175MHzでした。

- 上記結果より、内部の取り込みタイミングの時間関係はおよそ以下のようになっていると考えられます。今回のシステムの場合は、sdcTermでのサンプリングを内部クロックの立下りで行うよりも立ち上がりで行った方が動作周波数はより高速にできるということがわかりました[2]。

より高速動作を実現するために

- 上記の調整結果より、今回のシステムではFPGA内部の基本動作クロックとDDR3からのDQS入力の位相差が+5.5ns程度あると予想されます。現状の動作限界周波数はその周期が位相差に依存しており、位相差をより小さくすれば動作周波数を上げることは可能です。しかしながら現状の位相差でも、例えば動作周波数200MHz(周期5ns)で動作させることを考えた場合は以下のようなタイミングとなり、sdcTermでのサンプリングを内部クロックの再び立下りで行えばデータの取り込みが可能になると予想されます。

- しかしここで注意が必要なことは、上記タイミングではサンプリングする内部の立下りクロックは、位相差の基準立ち上がりクロックからは1.5クロックずれていますのでmasterモジュールに入ってくるデータ入力が通常のタイミングから1クロック遅れます。

したがってこのデータ遅れの調整を行うためにはリードアクノリッジ信号(rdAck)も遅らせる必要があります[3]。この考え方から、理論的にはリード時はデータとアクノリッジのタイミング調整を行えば、位相差にかかわらず動作周波数の高速化は可能になることがわかります[4]。

まとめ

- 今回の検証で、設計例 [DDR制御(論理)]で記述した内容を元に変更を行いFPGA評価キットを使用してDDR3アクセスの機能確認を実機にて行うことができました。

- 上記で記述した今回のタイミング調整により、DDR制御(論理)版ベースのソースコードではシステムの動作限界周波数がFPGA内部の基本動作クロックとDDR3からのDQS入力の位相差に依存しており、本システムの場合はそれが175MHzでした。また位相差を小さくすれば動作周波数の高速化を図れることがわかりました。

- 位相差に関係なく動作周波数の高速化を図るためには、リード時にデータとアクノリッジのタイミング調整を行えば良いことがわかりました。これにより当初目標にしていた動作周波数200MHzは達成することができました。汎用のDDR制御用IPコアではこの位相差を小さくすることと、リードデータ入力に対するアクノリッジ信号のタイミング調整をマイコンによりリアルタイムで行って高速・安定動作を実現しているものと思われます。

回路デザイン > 設計例 [DDR制御(実装)] > タイミング調整 このページのTOP ▲