全体像

- 使用するDDRは8bit、動作周波数は400MHz程度に絞ります。前者のパラメータはデータ長とアドレスマッピングの開始位置に影響します。後者のパラメータはDDRの選択[1]に影響します。

- 機能としてはバスブリッジに分類され、インターフェイスの端子と仕様はほぼ決まっています。Request, Dataパスは独立しているので、それぞれモジュールを分けて考えた方が楽です。

- 特にDataパスは、ハンドシェークがなく競合もないので、サイジングを行わないならほぼ直接繋ぐことができます[2]。一方、Requestパスはコマンドの発行と同時にデータタイミング(RLやWLのレイテンシなど)も集中して管理しなくてはなりません。従って、Requestパスを中心に話を進めたいと思います。

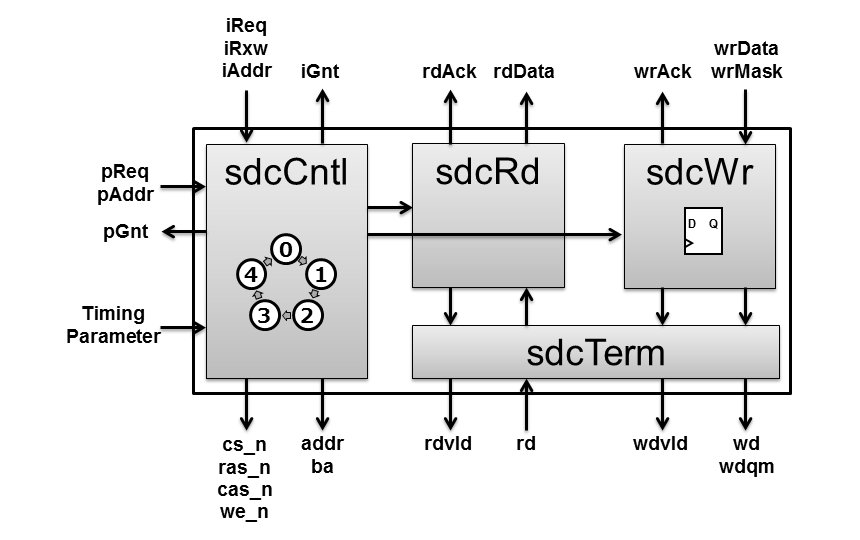

- 以下の4系統にモジュールを分けます。

- Request制御(sdcCntl):

ACタイミングをチェックしアクセス可能なら、アクセスパターン生成シーケンスが必要です。それによってコマンドを生成し、DDRの各端子をドライブします。バンクを含むアドレスマッピングもここで行います。

- Read Dataパス(sdcRd):

Request制御からコマンド発行のタイミングからRLサイクル遅延させてAcknowledgeを発生させます。そのタイミングに合わせるように、DDRからデータが返って来るのでマスターにそのまま返します。

- Write Dataパス(sdcWr):

Request制御からコマンド発行のタイミングからWLサイクル遅延させてAcknowledgeを発生させます。そのタイミングに合わせてマスターからデータを取得し、DDRへ渡します。Readと違ってデータは一旦ラッチするため[3]、Acknowledgeも一歩先んじて生成します。

- DDR Dataパス(sdcTerm):

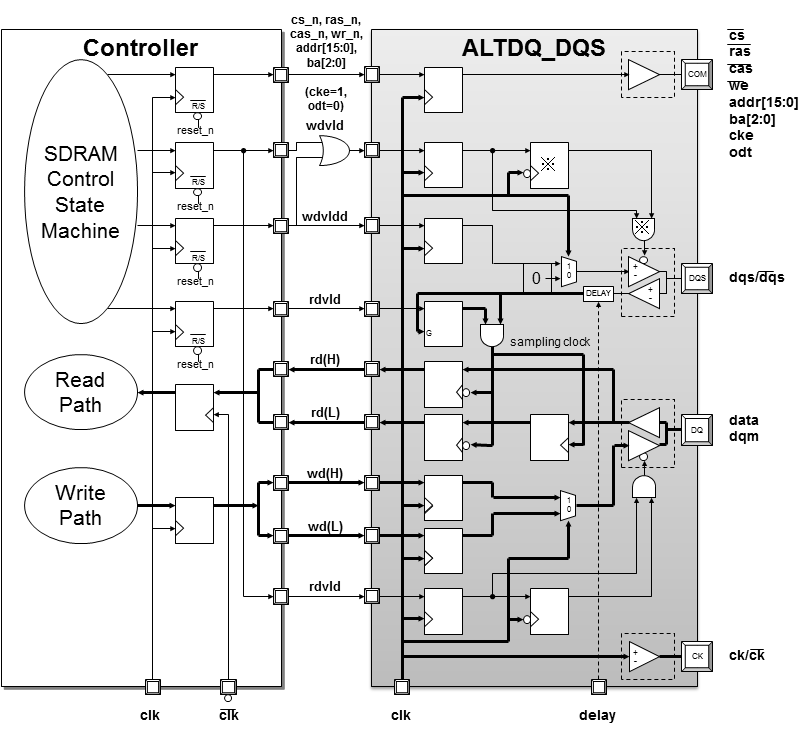

DDRに直接インターフェイスするPHY部分とのインターフェイスを取ります。それぞれの仕様に合わせて改変が必要になります。ここではAlteraのメガセルALTDQ_DQSを用いるものとします(DDR制御(実装)では打って変わってXilinxでお話します)。メガセルALTDQ_DQSの模式図を示しておきます。接続端子の概略は後述します。ただし、接続に関して今回設計するものとは微妙に異なります。詳細はテストをご覧下さい。

- R/W Dataパスには、入力信号からデータのアクセスタイミングが入ってこないので、Request制御からタイミングを取得する必要があります。しかし、他のモジュールとの接続はこれだけです。全体像を示しておきます。

- 通常アクセスの信号には接頭辞iを付けています。また、割り込みアクセスの信号には接頭辞pを付けています。PHYとのインターフェイスは信号名通りですが、rdvldとwdvldは、PHY内部のRead DataパスとWrite Dataパスのラッチタイミングです(wdvldの遅延信号wdvlddも必要)。

- 制御速度を考えると、DDRおよびPHYに接続する信号は基本的にFF出力にします。入力もなるべく論理を通さないようにします。クロックは単一ですが、sdcTerm内部でPHYとのタイミング調整を行うため、クロックの逆エッジ[4]を使用することになります。

Request制御モジュール(sdcCntl)について

- レイテンシ1のステートマシンを組み込みます。ステートマシンは400MHz動作程度に耐える必要があるので、論理はあまり深くしないように注意します。

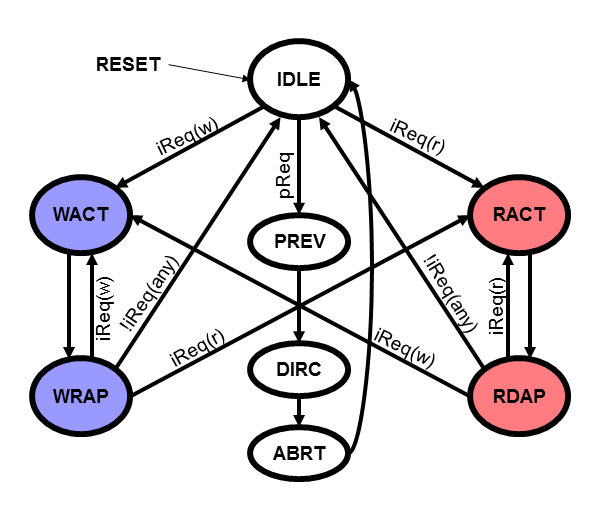

- 通常アクセスと割り込みアクセスの2つを明確に分け、前者は2つのコマンド発行(Activate→R/W)、後者は1つのコマンド発行(任意の端子アサート)を行うものとします。状態遷移図[5]を示します。RACTとWACTはActivate(R/W)、RDAPとWRAPはAuto Pre-charge付きR/W、PREV, DIRC, ABRTと続くのは割込みアクセスの状態名です。DIRC状態で端子に任意の値をアサートします。

- これらには遷移するタイミングがあります。以下のタイミングをそれぞれのカウンターで作成します。

- evakOk : 通常コマンド発行許可(2サイクルに1回のNOP挿入後)、カウンターはstateWait

- wrOk : W→Rコマンドの許可(TAWR期間カウント後)、カウンターはstateCnt

- rdOk : R→Wコマンドの許可(TARW期間カウント後)、カウンターはstateCnt

- actOver : RRDとFAWを満足せずActivateコマンド拒否、カウンターはactFIFO

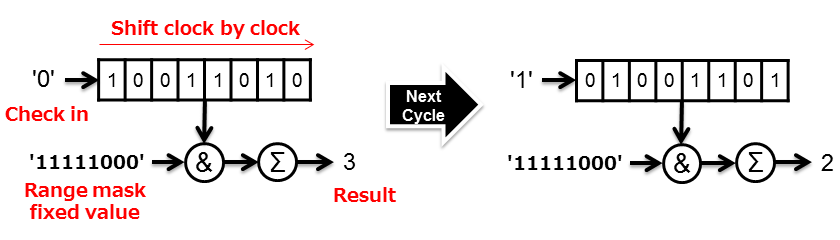

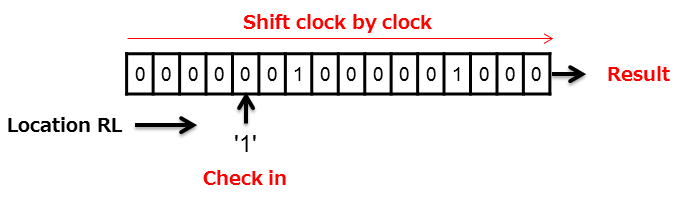

- actFIFOは、特殊なカウンターになるので説明します(R/W Dataパスにも同様のカウンターを使います)。特定区間の重ね合せは1つのカウンターで表現できないため、起動タイミングを記録するシフトレジスタを使います。起動するたびにフラグを立て、サイクルごとにシフトして記録を残します。シフトレジスタの特定区間(予めRRDやFAWからマスクを作っておく)の合計がその期間に占めるアクセス数になります。

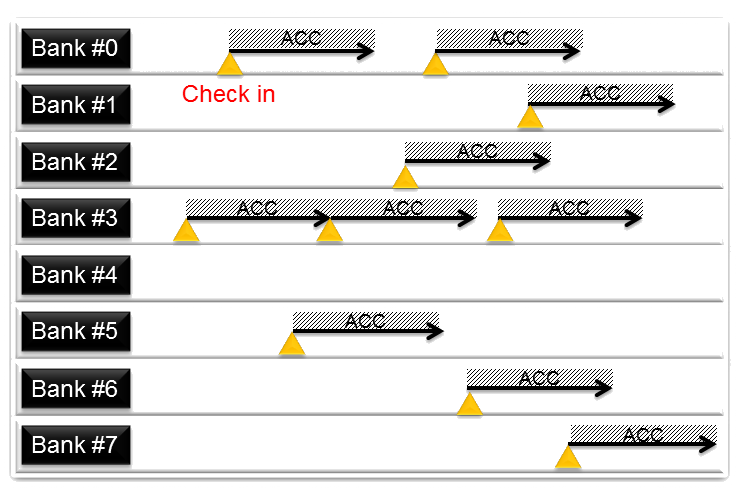

- 次に、アクセスそのものをマスクするフラグiTermを用意します。バンクごとの禁止区間を示すフラグで、バンク使用のスケジュール表になります。入力アドレスに含まれるバンクアドレスで検索し、フラグが立っていればリクエスト信号そのものをマスクします。バンクごとにカウンターを用意して生成します。

- このスケジュール表は、将来効果的なDDR制御を行う上で重要です。例えば、このフラグを用いて、最適なアクセスを行うようマスター側にフィードバックできます。従って、ステートマシンにはあえて入れません。図は、バンクごとのiTermがリクエストを受け付けるたびにカウントがセットされ、ACC分カウントするまでフラグを保持することを表しています(当然R/WごとにACCは異なる)。フラグがない部分へのアクセスはペナルティが発生しません。

- パラメータは制御途中で変えられるとよくないので、ステートマシンがIDLEのときにラッチします。従って、DDRの制御が一旦終了するまで、パラメータを変えても反映しない仕様です。ここはシステム依存なので、それぞれ所望のものに変えて下さい。

- 割り込みアクセスに関しては通常アクセスとは異なり、コマンドを発行していいタイミングに、iAddrの値をそのまま出力信号へアサインするだけにします。状態遷移も非常に簡単になります。こうすることによって、任意のコマンドがDDRに送信できます。

- 任意のコマンドにはリフレッシュも含みます。つまり、割り込みアクセスには初期化を含めインテリジェンスな制御が必要です。ここではインターフェイスのみ提示しますが、実際にはCPUなどから直接アクセスする必要が出てくるでしょう。また、それにさらに割り込んでタイマー駆動によるAuto-refreshコマンドを発行[6]することになります。

- 高速動作を意識して、回路規模を犠牲にして冗長になっても論理段数を少なくことにします。最終出力のcs_n信号に至るまでに、中間的な状態をFFで表すことができるものはできるだけラッチします(いくつかのOne hot信号が出来る)。各カウンタの生成も同じです。

- ただし、マスターインターフェイスに対するgntなどの信号は、分かりやすさを優先して遅延に関する工夫はしないことにします。マスターの作り方次第で、将来変えるべきポイント[7]になります。

Read Dataパスモジュール(sdcRd)について

- 前述したように、データはラッチしません。sdcTermモジュールから来るデータをそのままマスターに返すだけです。それに必要なAcknowledge系の信号を生成するだけになります。

- sdcTermに返すrdvldは、sdcTerm内でラッチタイミングとして使用するため、マスターに返すiRdAckに比べ1サイクル先行しますが、基本的に同じ信号と言えます。

- 生成は、Request制御モジュールで述べたactFIFOと同じ仕組みのカウンターを使います。若干異なりますが、図を見て頂くと分かるように、コマンド発行タイミングでRLをインデックスとした部分を1にセットします。そして、シフトアウトした1bitは、RL遅延したAcknowledgeとして使用します。これによよよって、複数のAcknowledgeが管理できます。

- DDRへコマンドを発行したタイミングは、Request制御モジュールから取得します。このタイミングは基本的にcas_n信号と同期します(RLサイクル後にデータが来る勘定になる)。

- Acknowledgeのタネをシフトレジスタから得た後、それをバースト分拡大します。単に、4サイクル延ばすだけです(8バーストが4サイクルになって返ってくる)。

Write Dataパスモジュール(sdcWr)について

- 設計思想はRead Dataパスと同じですが、マスターから来るデータとマスクを一旦ラッチします。

- タイミングはこのラッチ分の遅延と、PHYの遅延を考慮[8]しなければなりません。ここでは4を見積もって設定したWLから引いておきます(引く箇所はsdcCntl)。

DDR Dataパスモジュール(sdcTerm)について

- 選択したPHYは、8bitデータをサイジングして16bitにしてくれます。サイクルも単一クロックと同じ周期です。

- しかし、PHYのデータのラッチに使用するクロックは、DDRが出力するDQSに相当します。DLLを使って同期合わせしているとは言え、制御に使用するクロックと同じとは言えません。このため、一旦クロックの逆エッジでサンプリングし、すぐさま普通にサンプリングし直すことにします。

- PHYに必要なバッファ操作の信号(バッファのOpenやDouble Rateの切り替えなど)を整えます。PHYの仕様に合わせます。

回路デザイン > 設計例 [DDR制御(論理)] > 実装にあたって 次のページ(コーディング1) このページのTOP ▲