Arbitration

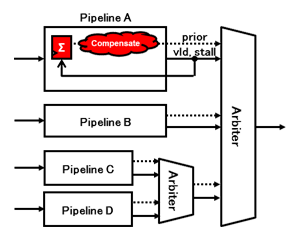

- Output arbitration of multiple pipelines, is a must for a guarantee for order of processing or resource sharing

- Grouping andInput control type for throughput controlare applied. Therefore take care of stage type for first stage

- Arbitration method[1] are various. For example the methods most used are as follows

- Arbitration determined method

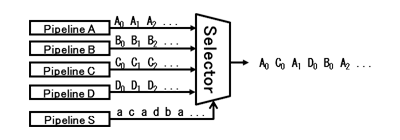

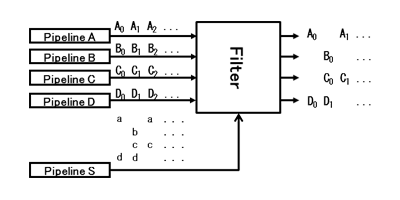

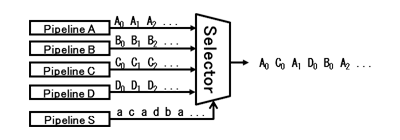

Refer to pipeline propagating pipeline branch order, it is used for re-ordering process order at the time of grouping.

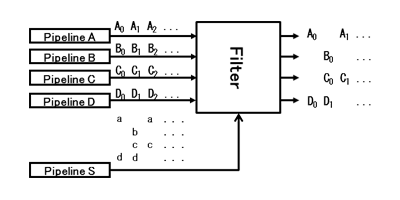

- Arbitration information pipeline for propagation is readied, and based on specified number execution is selected.

- Arbitration information pipeline for propagation is readied, and based on specified vector filter is executed.

- Arbitration non-determined method

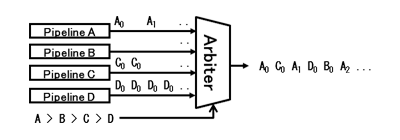

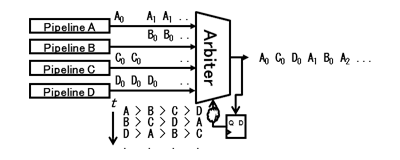

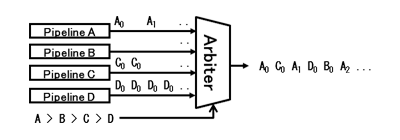

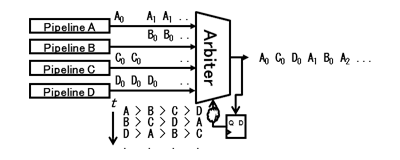

Used when result of multiple pipelines is selected and particular pipeline is processed.

- Perform selection based on specified priority.

- Perform selection based on specified priority(result to feedback to the next instruction)

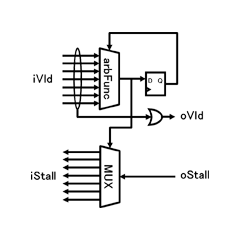

- Aribiter is close to the action of Groupingso both Valid which initiates the pipeline and Stall which controls the pipeline is required. Therefore, need to take care of accumulation of delay in loop[2]based on FF not output Valid, or logical stages which require Stall There are many times that delay control of loop is resolved by inserting at previous stage, depth of 2FIFOright after arbiter.

Regarding appropriate arbitration

- Similar to the world of communicationく[3],there are several methods of control of arbitration service for pipelines. Out of these, will elaborate on priority control and bandwidth control. Priority control and bandwidth control are not used separately but are combined and use efficiently.

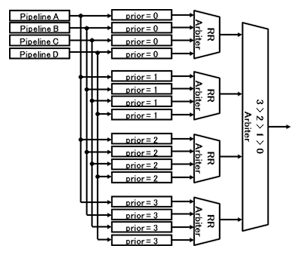

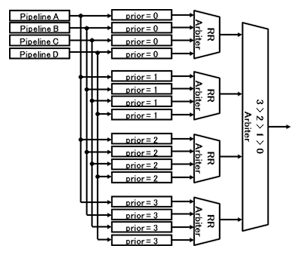

- In priority control, priority is attached to ech pipeline request. Priority is relatively evaluated under arbitration, and the one with higher priority is selected. When there are multiple cases with the same priority, then based on the specification of arbitration, are selected randomly (including round robin) as well as are selected in the order of pipeline numbers. Diagram below is an example of 4 pipelines having arbitrary priorities (4 levels), and one of them is selected by the arbiter in round robin method as well as ascending order.

- The priority of case where time restrictions are severe and delays are not tolerated have higher priority, and cases of best effort have lower priorities. However for systems in which there is a large bias towards the former which could affect the quality of the system (application is awkward), bandwidth restrictions are used to resolve the bias.[4]。

- Bandwidth restrictions are also several types, here method whereby priority is dynamically conrolled and reaches target bandwidth is elaborated.

- in order to measure the bandwidth(Throughput), negotiation attempts per unit time are measured. For example, measured value for each 64 cycles is recorded, (older values are discarded), several values nearest to current time are added. Sometimes wait is executed in order to reduce the influence of farther values.

- Basic priority is raised or lowered depending on the difference between the set bandwidth and the measured bandwidth. Priority is required a minimum of 2 levels, and the priority of the target pipeline needs to be all the same priority.

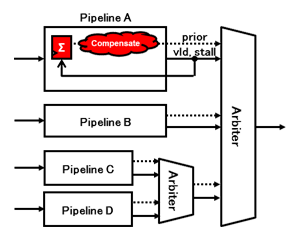

- Bandwidth measure and operation of priority is done at pipeline side considering the connection of arbiter.

- Bandwidth control is the control of the range of resources of arbiter that lead to bottleneck. Hence target bandwidth needs to fit inside the limits. Further, there are times when undetermined elements such as macro deviations are many, and set values need to keep changing.

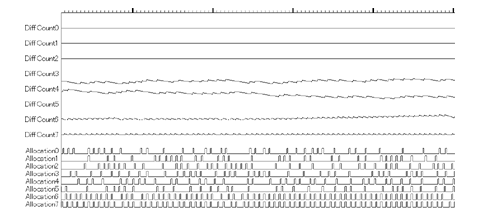

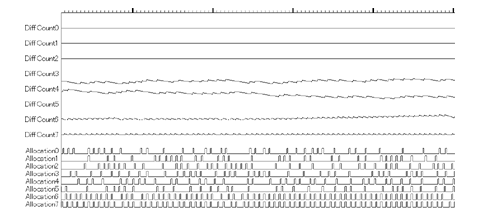

- Will show the simulation result of the above bandwidth control for reference. Test specification is as follows, and is an example of obtaining actual bandwidth very close to target bandwidth.

- Set target bandwidth at ratio of 2:2:4:4:8:8:15:16 in ascending order of 8 pipelines.

- Manage 3 levels of priority(2>1>0), and set basic to 1.

- When the target bandwidth is lower than a fixed amount, then increase the priority by +1, and when it is more than fixed amount, lower the priority by -1

- Valid of 8 pipelines to provide at random

- DiffCount is the difference between actual bandwidth and target bandwidth for unit time. (Measured values above or below the upper or lower limit are at a saturation due to the valid word length and hence are almost constant.)

- Allocation signifies arbitration is done.(Density is high when target bandwidth is high.)。

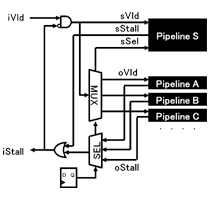

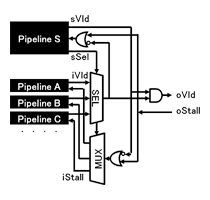

Sample RTL of arbitration determined method

| Routing |

- Propagate Valid to particular pipelike at branch. Simultaneously, to propagate selected variable sSel to another pipeline. Branch example is detour type.(sSel to increment for each negotiation.)。

- Select Valid for a particular pipeline at combination. Selection to be according to selection variable sSel

- Omit data code.

|

| Latency(CLK) | 0 |

module split(sVld, sStall, sSel, iVld, iStall, oVld, oStall, reset, clk);

output sVld;

input sStall;

output [R-1:0] sSel;

input iVld;

output iStall;

output [N-1:0] oVld;

input [N-1:0] oStall;

input reset;

input clk;

wire nasc = iVld & !iStall;

reg [R-1:0] sSel;

wire [N-1:0] vldVec = 1'b1 << sSel;

always @(posedge clk)

if (reset)

sSel <= #1 {R{1'b0}};

else if (!iStall)

sSel <= #1 sSel + 1'b1;

assign iStall = oStall[sSel] | sStall;

assign sVld = nasc;

assign oVld = {N{nasc}} & vldVec;

endmodule

|

| iVld → oVld | Propagate |

| iVld → iStall | Truncate |

| iStall ← oStall | Propagate |

|

| Latency(CLK) | 1 |

module unite(sVld, sStall, sSel, iVld, iStall, oVld, oStall);

input sVld;

output sStall;

input [R-1:0] sSel;

input [N-1:0] iVld;

output [N-1:0] iStall;

output oVld;

input oStall;

wire [N-1:0] StallVec = 1'b1 << sSel;

assign sStall = !iVld[sSel] | oStall;

assign iStall = {N{!sVld | oStall}} | ~StallVec;

assign oVld = iVld[sSel] & sVld;

endmodule

|

| iVld → oVld | Propagate |

| iVld → iStall | Propagate |

| iStall ← oStall | Propagate |

|

Sample RTL arbitration non-determined method

| Round-Robin Arbiter |

- From N Validsround robin method[5] is used to select 1

- Omit data code(oArb signal used to select 1 from N data)

- Round robin method pointer is arbitrated result close to detoured ascending order.

- Characteristics differ according to pointer detour method.

- When pointer is incremented each cycle, then approximately random arbitration is obtained.(Valid is equally processed.)

- When pointer is replaced by arbitration result + 1, then update type arbitration(Valid is equally processed.)

- When pointer is replaced by arbitration rsult, then parking type arbitration(Same Valid is continuously high priority)

|

| Latency(CLK) | 0 |

module rrArbiter(iVld, iStall, oVld, oStall, oArb, reset, clk);

parameter R = 3;

parameter N = 1<<R;

input [N-1:0] iVld;

output [N-1:0] iStall;

output oVld;

input oStall;

output [R-1:0] oArb;

input reset;

input clk;

reg [R-1:0] oPtr; // Round-Robin Pointer

wire [N-1:0] oVec = 1'b1 << rrArb;

// 0: Park, 1: Not Park

wire oInc = 1'b1;

always @(posedge clk)

if (reset)

oPtr <= #1 {R{1'b0}};

else if (oVld & !oStall)

oPtr <= #1 oArb + oInc;

assign iStall = {N{oStall}} & ~oVec;

assign oVld = |iVld;

assign oArb = arbFunc(iVld, oPtr);

function [R-1:0] arbFunc;

input [N-1:0] vld;

input [R-1:0] ptr;

reg [R-1:0] idx;

reg [R-1:0] num[N-1:0];

integer i, j;

begin

for (i=0; i<N; i=i+1) begin

num[i] = {R{1'bx}};

for (j=0; j<N; j=j+1) begin

idx = i[R-1:0] + ~j[R-1:0];

if (vld[idx])

num[i] = idx;

end

end

arbFunc = num[ptr];

end

endfunction

endmodule

|

| iVld → oVld | Propagate |

| iVld → iStall | Propagate |

| iStall ← oStall | Propagate |

|

Logical Design Circuit > Pipeline > Arbitration Next Page(Synchronizatin) TOP of this page ▲

[1]

Carefully examining the RTL, depending on each arbitration method

Basic typeor to use

Buffer type differs. In buffer type, FF which can be buffered are limited and hence cannot accomodate multiple versus 1.