/* **************************** MODULE PREAMBLE ********************************

Copyright (c) 2012, ArchiTek

This document constitutes confidential and proprietary information

of ArchiTek. All rights reserved.

*/

// ***************************** MODULE HEADER *********************************

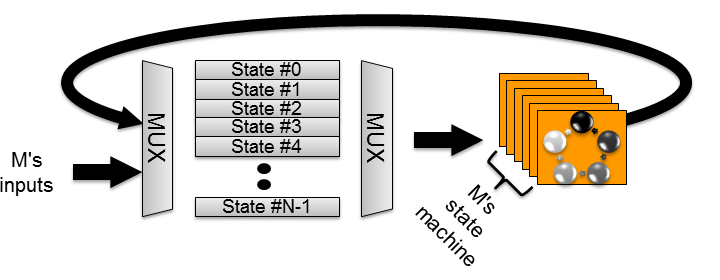

module state (

iPtr, iAct, iInit, iLoop,

sPtr, sDone,

aPtr, aDone,

lPtr, lDone,

cPtr, cDone, cFin,

pPtr, pDone, pFin,

stat0, stat1, stat2,

reset, clk

);

// ************************ PARAMETER DECLARATIONS *****************************

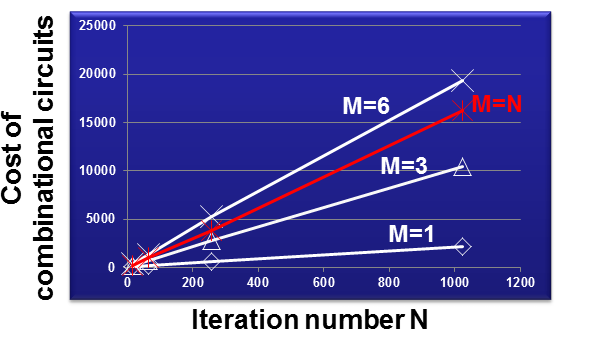

parameter CNR = 6; // Number Radix

parameter CN = 1<<CNR;

// *************************** I/O DECLARATIONS ********************************

// Input

input [CNR-1:0] iPtr;

input iAct;

input iInit;

input iLoop;

// Selector

input [CNR-1:0] sPtr;

input sDone;

// Arbiter

input [CNR-1:0] aPtr;

input aDone;

// Loader

input [CNR-1:0] lPtr;

input lDone;

// Command

input [CNR-1:0] cPtr;

input cDone;

input cFin;

// Pipeline

input [CNR-1:0] pPtr;

input pDone;

input pFin;

// State Output

output [CN-1:0] stat0;

output [CN-1:0] stat1;

output [CN-1:0] stat2;

// Utility

input reset;

input clk;

// ************************** LOCAL DECLARATIONS *******************************

wire [CN-1:0] iActVec = ('b1 << iPtr) & {CN{iAct}};

wire [CN-1:0] iInitVec = ('b1 << iPtr) & {CN{iInit}};

wire [CN-1:0] iLoopVec = ('b1 << iPtr) & {CN{iLoop}};

wire [CN-1:0] sDoneVec = ('b1 << sPtr) & {CN{sDone}};

wire [CN-1:0] aDoneVec = ('b1 << aPtr) & {CN{aDone}};

wire [CN-1:0] lDoneVec = ('b1 << lPtr) & {CN{lDone}};

wire [CN-1:0] cDoneVec = ('b1 << cPtr) & {CN{cDone}};

wire [CN-1:0] cFinVec = ('b1 << cPtr) & {CN{cFin}};

wire [CN-1:0] pDoneVec = ('b1 << pPtr) & {CN{pDone}};

wire [CN-1:0] pFinVec = ('b1 << pPtr) & {CN{pFin}};

reg [CN-1:0] stat0, stat1, stat2;

reg [CN-1:0] stat0D, stat1D, stat2D;

integer i;

// ****************************** MODULE BODY **********************************

// -----------------------------------------------------------------------------

// State Machine

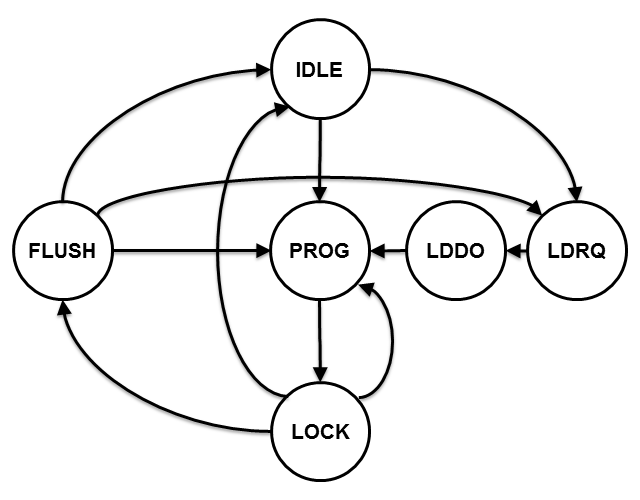

parameter IDLE = 3'h0,

LOCK = 3'h2,

FLUSH = 3'h3,

PROG = 3'h4,

LDRQ = 3'h6,

LDDO = 3'h7;

always @(posedge clk) for (i=0; i<CN; i=i+1)

if (reset)

{stat0[i], stat1[i], stat2[i]}

<= #1 IDLE;

else

{stat0[i], stat1[i], stat2[i]}

<= #1 {stat0D[i], stat1D[i], stat2D[i]};

always @(

stat0 or stat1 or stat2 or

iActVec or iInitVec or iLoopVec or

sDoneVec or

aDoneVec or

lDoneVec or

cDoneVec or cFinVec or

pDoneVec or pFinVec

) for (i=0; i<CN; i=i+1) begin

{stat0D[i], stat1D[i], stat2D[i]}

= {stat0[i], stat1[i], stat2[i]};

case ({stat0[i], stat1[i], stat2[i]})

IDLE: if (iActVec[i])

case (iInitVec[i])

1'b0: {stat0D[i], stat1D[i], stat2D[i]} = PROG;

1'b1: {stat0D[i], stat1D[i], stat2D[i]} = LDRQ;

endcase

LDRQ: if (sDoneVec[i])

{stat0D[i], stat1D[i], stat2D[i]} = LDDO;

LDDO: if (lDoneVec[i])

{stat0D[i], stat1D[i], stat2D[i]} = PROG;

PROG: if (aDoneVec[i])

{stat0D[i], stat1D[i], stat2D[i]} = LOCK;

LOCK: if (cDoneVec[i])

casex ({cFinVec[i], iActVec[i]})

2'b00: {stat0D[i], stat1D[i], stat2D[i]} = IDLE;

2'b01: {stat0D[i], stat1D[i], stat2D[i]} = PROG;

2'b1x: {stat0D[i], stat1D[i], stat2D[i]} = FLUSH;

endcase

FLUSH: if (pDoneVec[i] & pFinVec[i])

casex ({iLoopVec[i], iInitVec[i], iActVec[i]})

3'b0xx,

3'b1x0: {stat0D[i], stat1D[i], stat2D[i]} = IDLE;

3'b101: {stat0D[i], stat1D[i], stat2D[i]} = PROG;

3'b111: {stat0D[i], stat1D[i], stat2D[i]} = LDRQ;

endcase

endcase

end

// ************************** FUNCTIONS and TASKS ******************************

endmodule

// *****************************************************************************