結合

- パイプラインどうしの結合[1]は、高機能化・低コスト化に必要不可欠です。例えば、1つの座標からメモリアクセスと座標変換を並列に行い両者の結果を演算するなど、多くの場合で使用します。

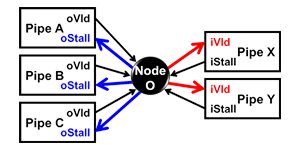

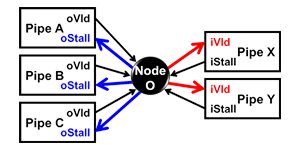

- ノードOにおいて、それぞれパイプラインの終端ステージのoVld, iStallを用いて、新たなiVld(下図赤色), oStall(下図青色)を生成します。

- ノードOにおける必要十分条件(NASC)は次式になります。ノードをモジュールとして想定しているため、接頭辞が逆転していることに注意して下さい(例えば、Pipe AのoVldは、Node OのiVld)。

| NASCO = |

N-1

Π

i=0 |

iVldi |

M-1

Π

i=0 |

oStalli |

ここで、NとMはそれぞれ前段と後段の結合数[2] |

単純な結合方式サンプルRTL

| 単純な結合方式 |

- 必要十分条件(NASC)が真であれば、結合後のoVldを全てアサートし、結合前のiStallを全てデアサート。

- iStalliには自らのiVldiが関わるため、前段ステージにバッファ型(S?)以外のものを用いると、iVldiは永遠にデアサート状態となり機能しない。

- oVldiには自らのoStalliが関わるため、後段ステージにスループット制御を行う入力制御タイプを用いると、ループした組み合わせ回路[3]が発生。

|

module node(iVld, iStall, oVld, oStall);

parameter N = 4;

parameter M = 4;

input [N-1:0] iVld;

output [N-1:0] iStall;

output [M-1:0] oVld;

input [M-1:0] oStall;

wire nasc = (&iVld) & (~|oStall);

assign iStall = {N{~nasc}};

assign oVld = {M{nasc}};

endmodule

|

一般的な結合方式サンプルRTL

| 一般的な結合方式 |

- 必要十分条件(NASC)が真であれば、結合後のoVldを以下の条件でアサートし、結合前のiStallを以下の条件でデアサート。

- iStalliには自らのiVldiの関与を排除

- oVldiには自らのoStalliの関与を排除

- この条件下でも、後段ステージにスループット制御を行う入力制御タイプを複数用いると、ループした組み合わせ回路[3]が発生。

|

module node(iVld, iStall, oVld, oStall);

parameter P = 2;

parameter Q = 2;

parameter M = 1<<P;

parameter N = 1<<Q

input [N-1:0] iVld;

output [N-1:0] iStall;

output [M-1:0] oVld;

input [M-1:0] oStall;

reg [N-1:0] iStall;

reg [M-1:0] oVld;

integer i;

always @(iVld or oStall)

for (i=0; i<N; i=i+1)

iStall = ~&vldSerFunc(iVld, i) | (|oStall);

always @(iVld or oStall)

for (i=0; i<M; i=i+1)

oVld = &iVld & (~|StallSerFunc(oStall, i));

function [N-1:0] vldSerFunc;

input [N-1:0] vld;

input [Q-1:0] num;

integer i;

for (i=0; i<N; i=i+1)

vldSerFunc[i] = (i == num) ? 1'b1 : vld[i];

endfunction

function [M-1:0] StallSerFunc;

input [M-1:0] Stall;

input [P-1:0] num;

integer i;

for (i=0; i<M; i=i+1)

StallSerFunc[i] = (i == num) ? 1'b0 : Stall[i];

endfunction

endmodule

|

回路デザイン > パイプライン > 結合 次のページ(スループット制御) このページのTOP ▲