/* **************************** MODULE PREAMBLE ********************************

Copyright (c) 2012, ArchiTek

This document constitutes confidential and proprietary information

of ArchiTek. All rights reserved.

// 基本クロックを生成する最上位モジュール*/

// ***************************** MODULE HEADER *********************************

`timescale 1ps / 1ps

module test;

// ************************ PARAMETER DECLARATIONS *****************************

parameter D = 1;

parameter DCLK = 5000;

parameter DCLK2 = DCLK/2;

// ************************** LOCAL DECLARATIONS *******************************

reg clk;

reg reset_n;

// ****************************** MODULE BODY **********************************

// -----------------------------------------------------------------------------

initial begin clk=0; forever begin #(DCLK2) clk=~clk; end end

// -----------------------------------------------------------------------------

initial begin reset_n=0; #D reset_n=0; #(DCLK*3.5) reset_n=1; end

// -----------------------------------------------------------------------------

top top_0 (

clk, reset_n,

);

// ************************** FUNCTIONS and TASKS ******************************

endmodule

// *****************************************************************************

/* **************************** MODULE PREAMBLE ********************************

Copyright (c) 2012, ArchiTek

This document constitutes confidential and proprietary information

of ArchiTek. All rights reserved.

*/

// ***************************** MODULE HEADER *********************************

module top (

clk, reset_n

);

// ************************ PARAMETER DECLARATIONS *****************************

シミュレーション時間を指定

parameter ST = 2500000; // Simulation interval

// ***************************** I/O DECLARATIONS ******************************

input clk;

input reset_n;

// ************************** LOCAL DECLARATIONS *******************************

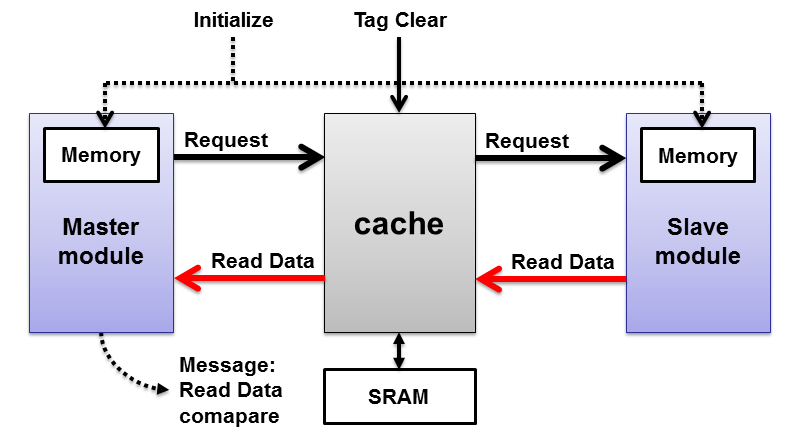

マスターRequest信号

wire iReq, iGnt, iRxw;

wire [31:0] iAddr;

マスターWrite信号(使用しない)

wire iWrStrb;

wire iWrAck = 1'b0;

wire [31:0] iWrData;

wire [3:0] iWrMask;

マスターRead信号

wire iRdStrb, iRdAck;

wire [31:0] iRdData;

スレーブRequest信号

wire oReq, oGnt;

wire [31:0] oAddr;

スレーブRead信号

wire oStrb, oAck;

wire [31:0] oData;

タグ操作信号

reg aReq;

wire aGnt;

2ポートSRAM信号

wire ramWE, ramRE;

wire [9:0] ramWA, ramRA;

wire [31:0] ramWD, ramRD;

// シミュレーション用変数

reg [1:0] rst;

reg reset;

初期化テンポラリ(バースト長4)

reg [31:0] d0, d1, d2, d3;

integer i;

// ******************************** MODULE BODY ********************************

// -----------------------------------------------------------------------------

// Reset

always @(posedge clk or negedge reset_n)

if (!reset_n)

rst <= #1 2'b11;

else

rst <= #1 {rst[0], 1'b0};

always @(posedge clk or negedge reset_n)

if (!reset_n)

reset <= #1 1'b1;

else

reset <= #1 rst[1];

// -----------------------------------------------------------------------------

// Master

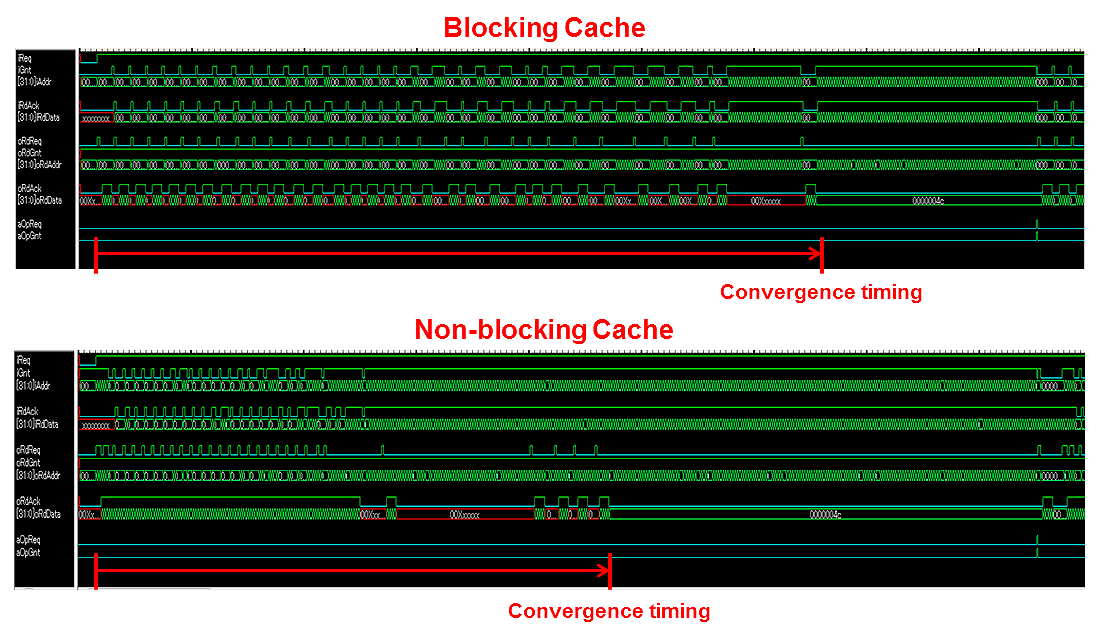

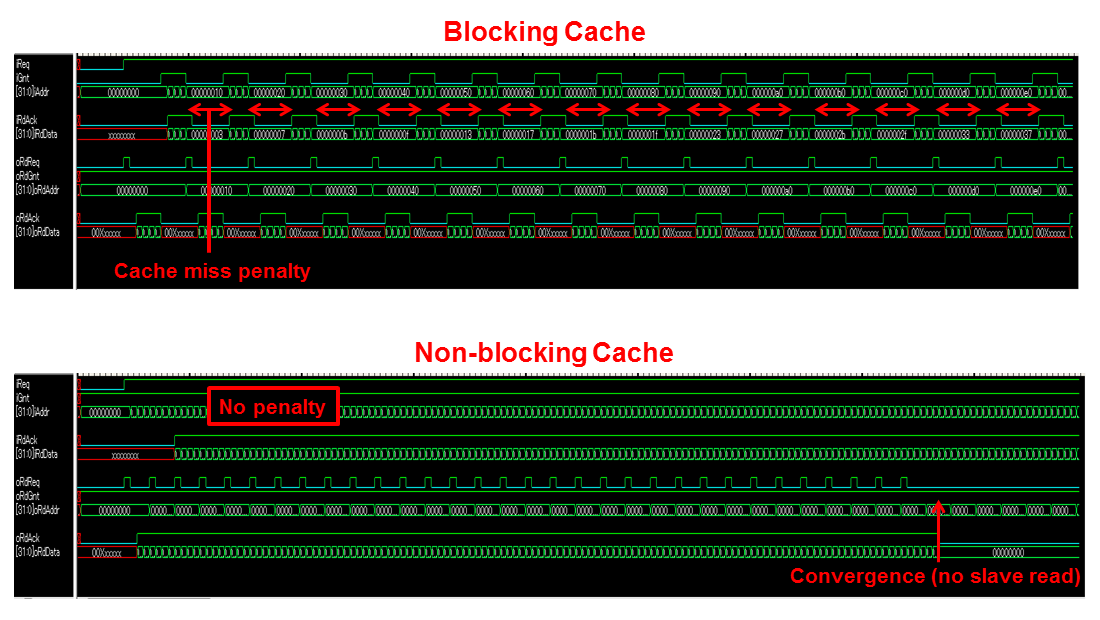

マスターをアドレス範囲512Byte以内でコール

master #(32'h000001fc) master_0 (

.req (iReq),

.gnt (iGnt),

.rxw (iRxw),

.addr (iAddr),

.wrStrb (iWrStrb),

.wrAck (iWrAck),

.wrFlush (1'b0),

.wrData (iWrData),

.wrMask (iWrMask),

.rdStrb (iRdStrb),

.rdAck (iRdAck),

.rdFlush (1'b1),

.rdData (iRdData),

.omit (1'b0),

.reset (reset),

.clk (clk)

);

// -----------------------------------------------------------------------------

// Slave

スレーブをコール

slave slave_0 (

.req (oReq),

.gnt (oGnt),

.rxw (1'b1),

.burst (2'h3),

.addr (oAddr),

.wrStrb (1'b0),

.wrAck (),

.wrData (32'd0),

.wrMask (4'd0),

.rdStrb (oStrb),

.rdAck (oAck),

.rdData (oData),

.reset (reset),

.clk (clk)

);

// -----------------------------------------------------------------------------

// Cache Body

キャッシュをライン数256、バースト長4でコール

cache #(8, 2) cache_0 (

.iReq (iReq),

.iGnt (iGnt),

.iAddr (iAddr),

.iRdStrb (iRdStrb),

.iRdAck (iRdAck),

.iRdData (iRdData),

.oRdReq (oReq),

.oRdGnt (oGnt),

.oRdAddr (oAddr),

.oRdStrb (oStrb),

.oRdAck (oAck),

.oRdData (oData),

.aOpReq (aReq),

.aOpGnt (aGnt),

.dramWE (ramWE),

.dramWA (ramWA),

.dramWD (ramWD),

.dramRE (ramRE),

.dramRA (ramRA),

.dramRD (ramRD),

.reset (reset),

.clk (clk)

);

// -----------------------------------------------------------------------------

// SRAM (Dual Port 32bit x 1K)

キャッシュで使用する2ポートSRAM(32bit x 1024 = 4KByte)

dualSRAM #(32, 10) ram_0 (

.WE (ramWE),

.WA (ramWA),

.WD (ramWD),

.RE (ramRE),

.RA (ramRA),

.RD (ramRD),

.CK (clk)

);

// -----------------------------------------------------------------------------

// Initialize Master

マスターモジュール内部のSRAMをインクリメンタルデータに初期化

always @(negedge reset_n)

if (!reset_n)

for (i=0; i<'h40_0000/16; i=i+1) begin

d0 = 4*i;

d1 = 4*i+1;

d2 = 4*i+2;

d3 = 4*i+3;

master_0.mem[i] = {d3, d2, d1, d0};

end

// -----------------------------------------------------------------------------

// Initialize Slave

スレーブモジュール内部のSRAMをインクリメンタルデータに初期化

always @(negedge reset_n)

if (!reset_n)

for (i=0; i<'h40_0000/16; i=i+1) begin

d0 = 4*i;

d1 = 4*i+1;

d2 = 4*i+2;

d3 = 4*i+3;

slave_0.mem[i] = {d3, d2, d1, d0};

end

// **************************** FUNCTIONS and TASKS ****************************

initial #ST $finish;

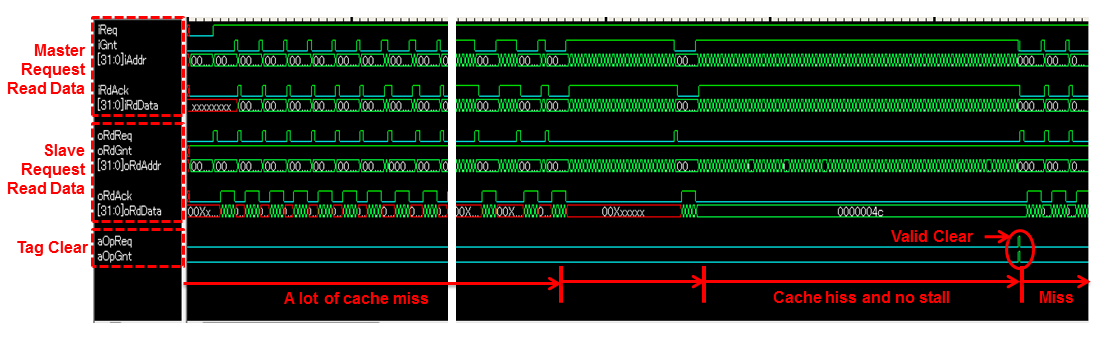

設定した遅延後にタグクリア

initial begin

#0000000 aReq = 1'b0;

#2000000 clear;

end

task clear;

begin

aReq = 1'b1;

@(negedge clk)

wait(aGnt);

@(posedge clk)

aReq = 1'b0;

end

endtask

endmodule

// *****************************************************************************