IP core

We offer a variety of IP cores, including IP with unique and original functions.

Below is an introduction to our main IP cores and examples of IP-based designs.

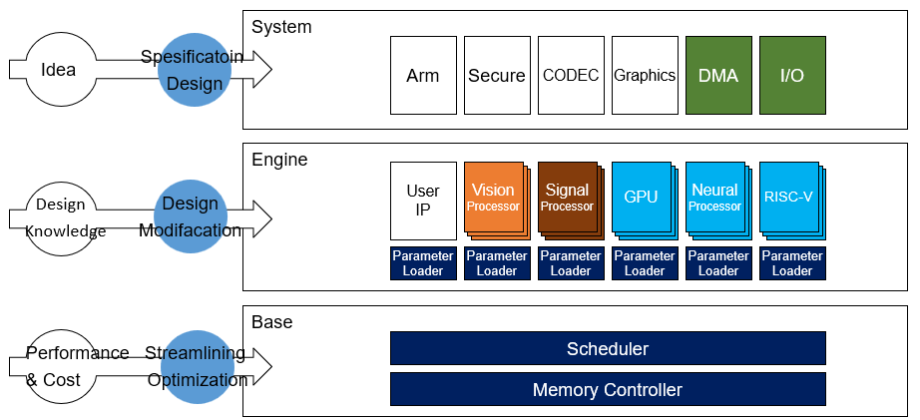

1.Sample Design Hierarchy

-

「Overall」:From ideas to specification and design

-

「Engine」:Design and customize engines using standard IPs

-

「Integration」:Optimize and streamline for performance and cost

2.IP families

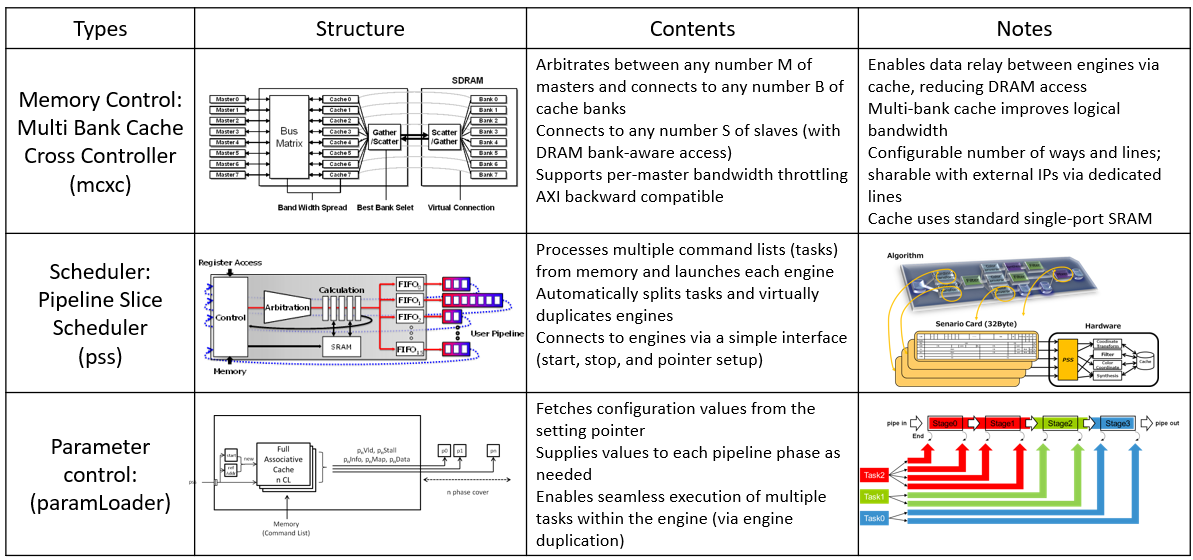

(1) Platform IP

mcxc

pss

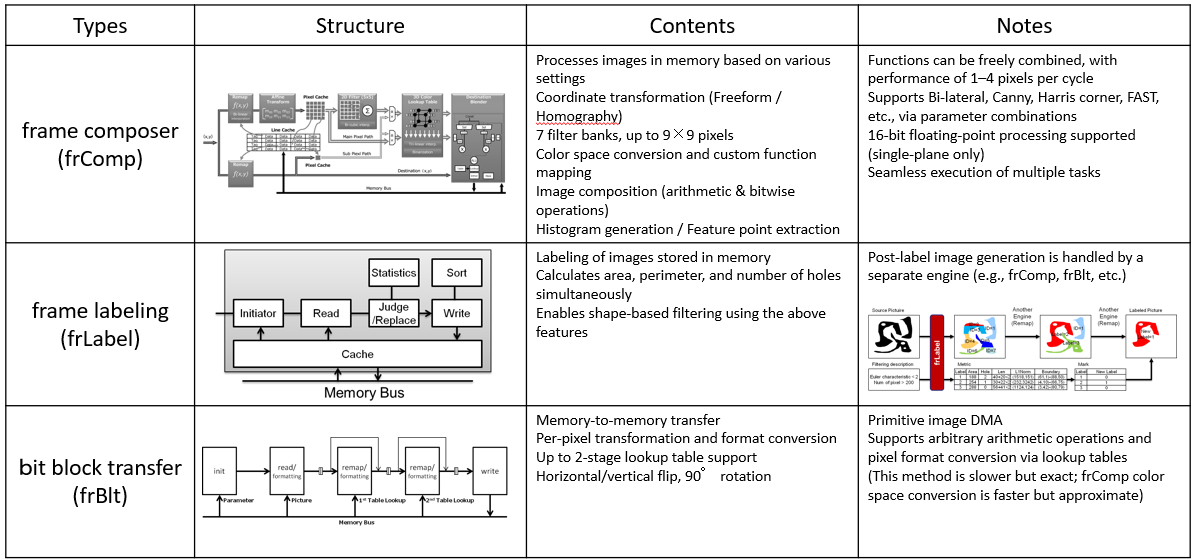

(2) Image Processing IP

※ Command list (parameters) is auto-fetched, with no pipeline bubbles between tasks

※ Best used with the pss scheduler, but also works standalone without issues

frComp

frLabel

frBlt

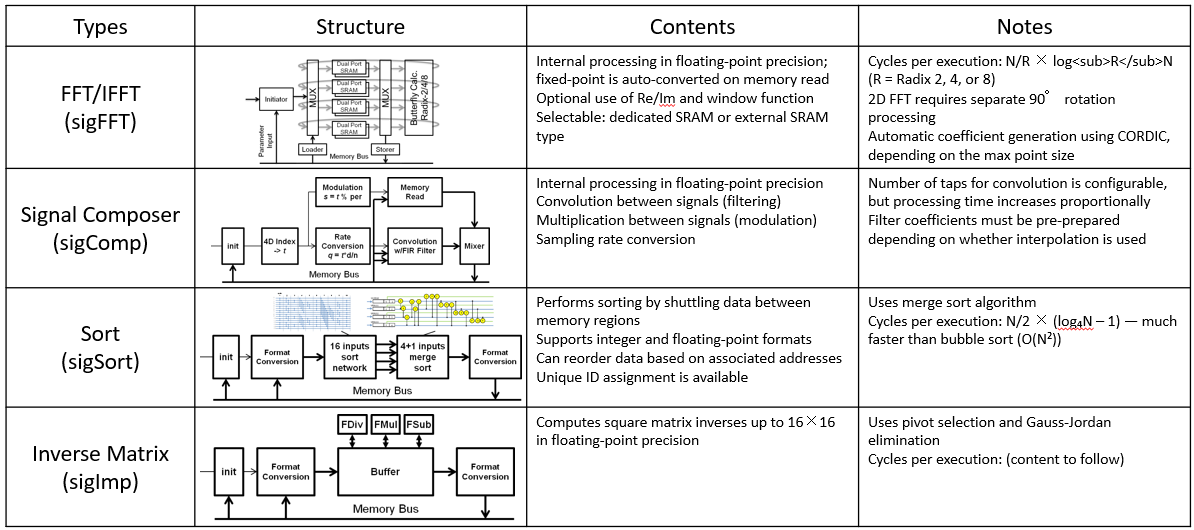

(3) Signal Processing IP

※ Command list (parameters) is auto-fetched, with no pipeline bubbles between tasks

※ Best used with the pss scheduler, but also works standalone without issues

sigFFT

sigComp

sigSort

sigImp

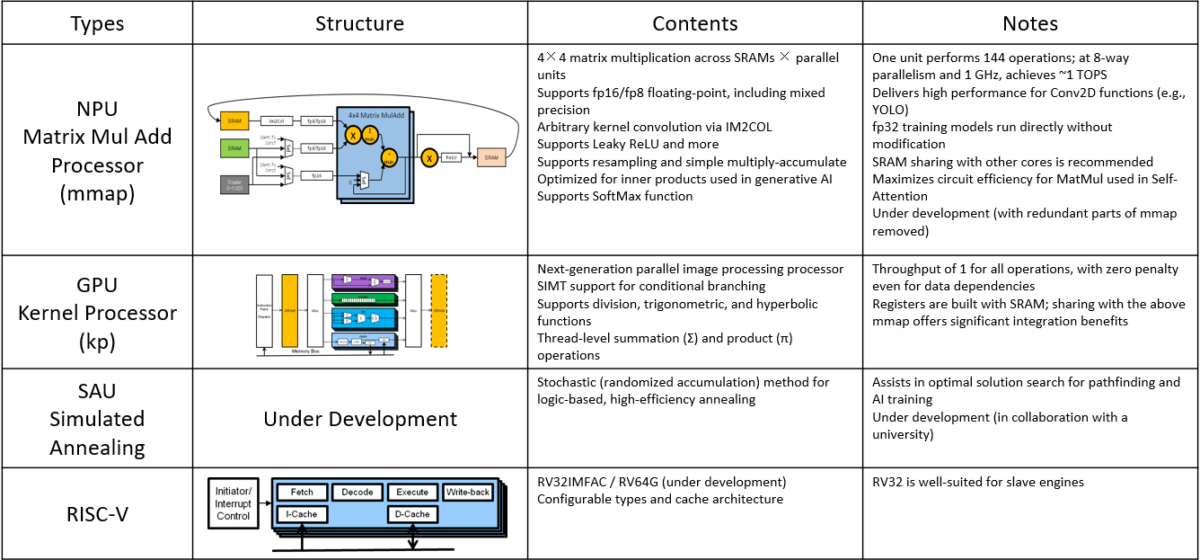

(4) AI・Processor IP

※Command list (parameters) is auto-fetched, with no pipeline bubbles between tasks

※ Best used with the pss scheduler, but also functions independently without issues

mmap

kp

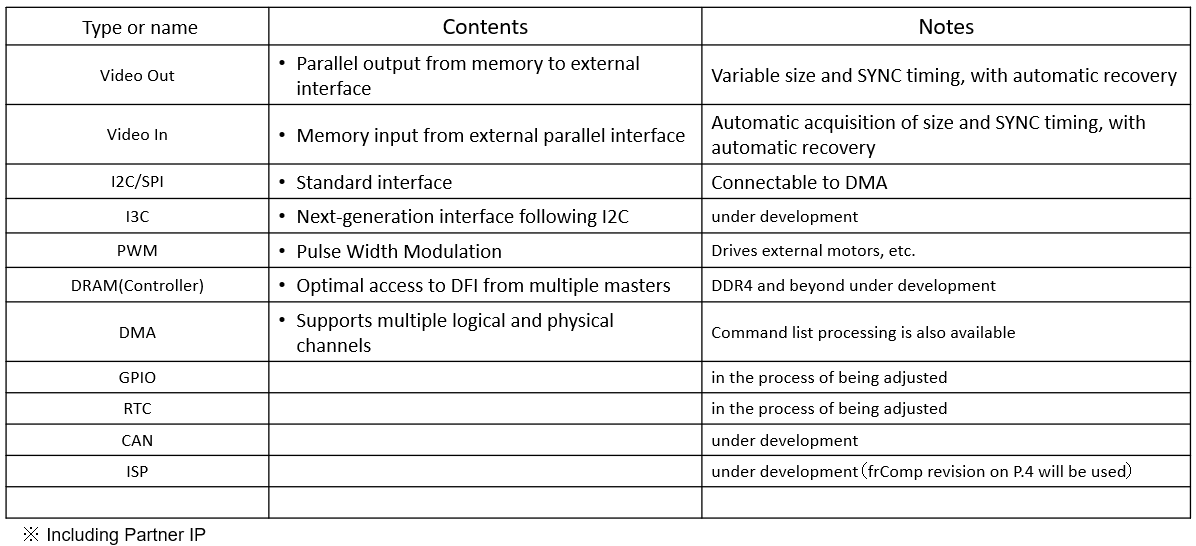

(5) I/O IP

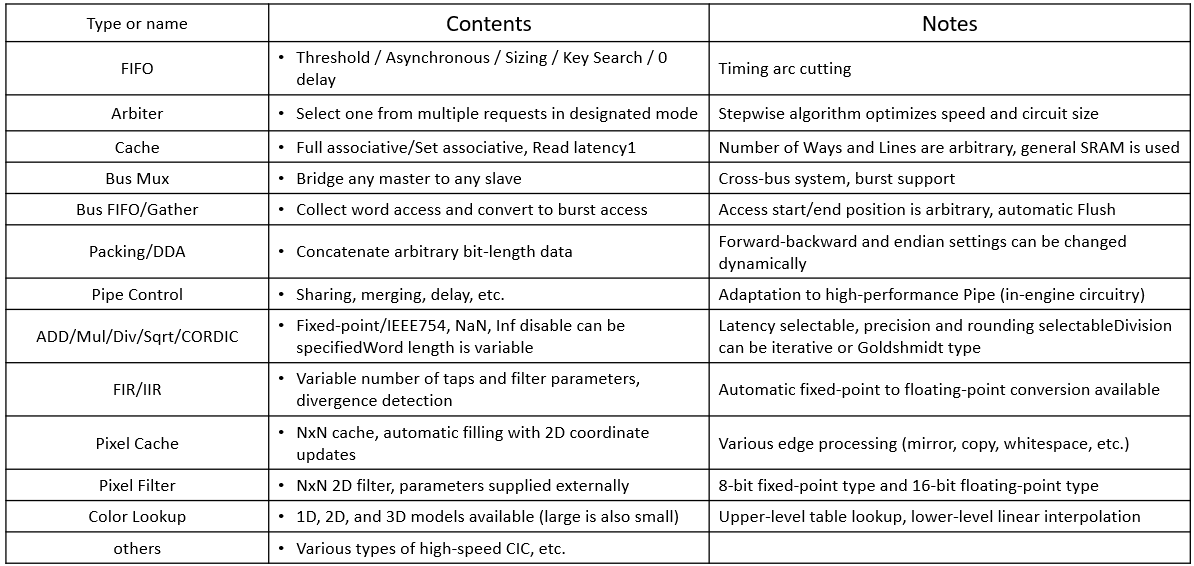

(6) General-purpose IP

3.Design examples utilizing IP

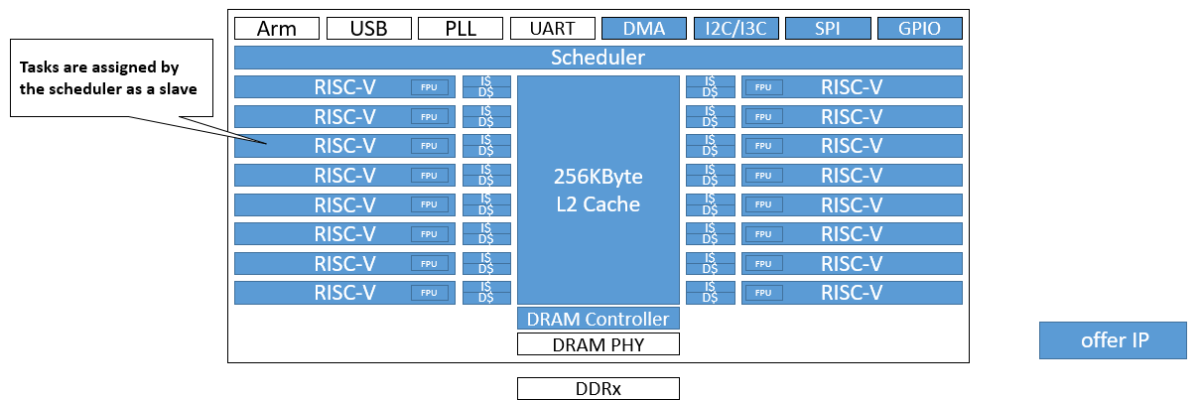

Example1:General-Purpose I/O Processing Chip (Homogeneous Type)

An I/O processing chip with low latency, controlled by software

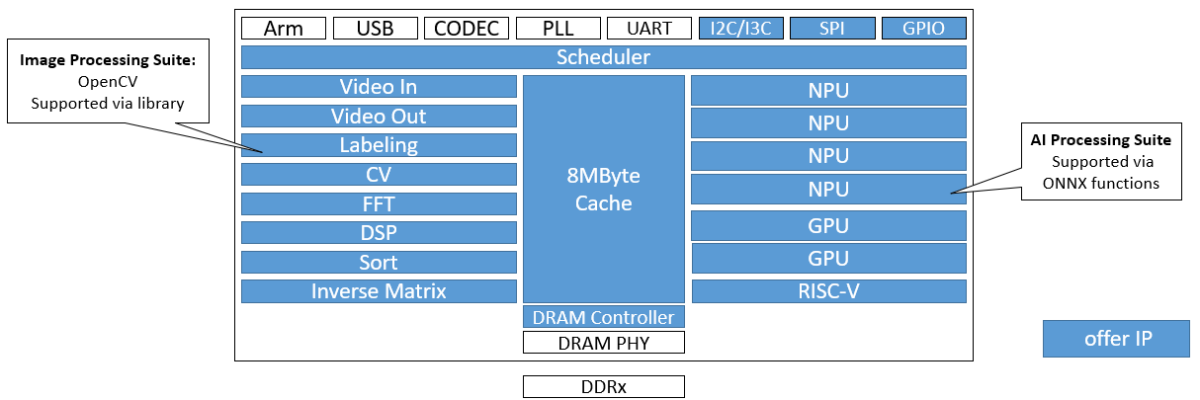

Example2:Edge AI / Image Processing Chip (Heterogeneous Type)

A high-performance, low-power chip integrating a dedicated engine and a general-purpose processor

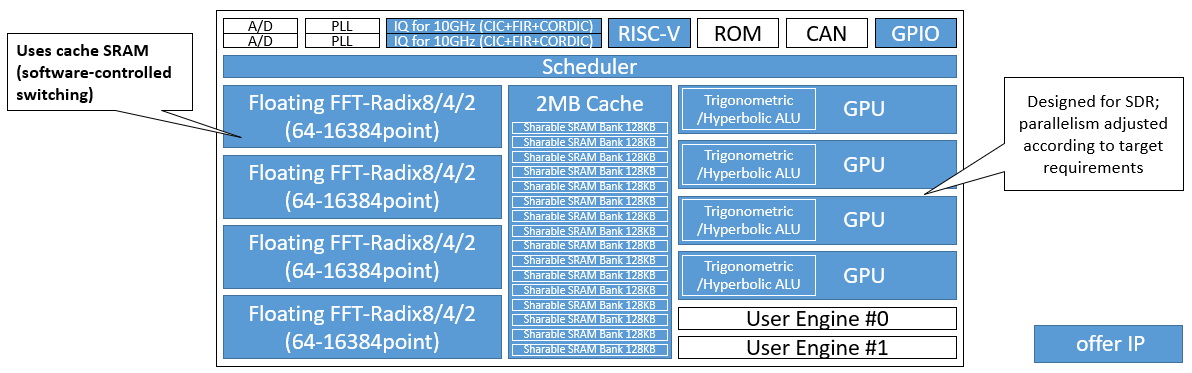

Example3:Programmable Radar Chip (Hybrid Homogeneous/Heterogeneous Architecture)

A high-performance chip capable of arbitrary combinations of high-speed frequency conversion and signal processing

※ All materials published or provided on this website are the property of our company (or the legitimate rights holder). Unauthorized reproduction, reprinting, or distribution is strictly prohibited.