# mmap Specification

Matrix Mul Add Processor

**Revision 0.2**

30 July 2025

English ver.

Copyright 2011 ArchiTek All Rights Reserved

**Confidential and Proprietary**

- 1. Overview

- 1.1. Introduction

- 1.2. Main Parameters

- 1.3. Implementation Parameters

- 2. Signal Lines

- 2.1. Control Bus Interface

- 2.2. PSS Interface

- 2.3. Memory Interface (Parameter Read Use)

- 2.4. SRAM Interface (WriteQ)

- 2.5. SRAM Interface (Read A/B)

- 2.6. SRAM Interface (Read/Write P)

- 2.7. Scalar Register Interface (A/B)

- 2.8. Utility

- 3. Configuration and Operation Description

- 3.1. Notation

- 3.2. Configuration Overview

- 3.3. Drive Interface (Initiator)

- 3.4. Fragmentation Precautions

- 3.5. Command Start and End

- 3.6. Floating Point Arithmetic

- 3.7. im2col Matrix Operations

- 3.8. Standard Matrix Operations

- 3.9. Hadamard Matrix Operations

- 3.10. Min/Max Function

- 3.11. Register File Structure

- 3.12. Parallel Circuits

- 3.13. Operational Erro

- 4. Control Register Description

- 4.1. Overview

- 4.2. Definition

- 4.3. Details

- 4.3.1.1. Reset Register

- 4.3.1.2. System Register

- 4.3.1.3. Control Register

- 4.3.1.4. Value Register

- 4.3.1.5. ConstAB Register

- 4.3.1.6. Select Register

- 4.3.1.7. Monitor Register

- 4.3.1.8. MonitorZW Register

- 4.3.1.9. MonitorST Register

- 4.3.1.10. MonitorID Register

- 4.3.1.11. BreakXY Register

- 4.3.1.12. BreakZW Register

- 4.3.1.13. BreakST Register

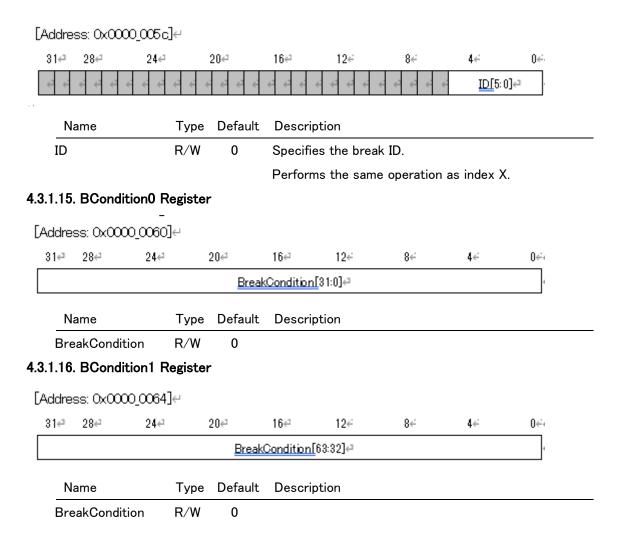

- 4.3.1.14. BreakID Register

- 4.3.1.15. BCondition0 Register

- 4.3.1.16. BCondition1 Register

- 5. Command List Description

- 5.1. Overview

- 5.2. Definition

- 5.3. Details

- 5.3.1.1 Cntl Command

- 5.3.1.2 Format Command

- 5.3.1.3 Offset Command

- 5.3.1.4. Gap Command

- 5.3.1.5. Size Command

- 5.3.1.6. Size Command

- 5.3.1.7. StepO Command

- 5.3.1.8. StepO Command

- 5.3.1.9. StepA Command

- 5.3.1.10. StepA Command

- 5.3.1.11. StepB Command

- 5.3.1.12. StepB Command

- 5.3.1.13. StepP Command

- 5.3.1.14. StepP Command

- 5.3.1.15. StepQ Command

- 5.3.1.16. StepQ Command

- 6. Application Note

- 6.1. Example Implementation

- 6.1.1. conv2d (im2col)

- 6.1.2. LUT Applied to the Final Output Value

### 1. Overview

#### 1.1. Introduction

- The Matrix Mul Add Processor (hereafter referred to as mmap) is a processor capable of

performing matrix operations with arbitrary kernel sizes using the im2col function. It is

particularly effective in convolution operations involving multiple input/output channels in

deep learning applications.

- It offers excellent functional and performance scalability, as it allows easy expansion of the computation pipeline, enhancement of computational precision, and finer pipeline pitch segmentation. This version utilizes both a 16-bit half-precision floating-point arithmetic unit and an 8-bit floating-point arithmetic unit.

- SRAM is required to repeatedly perform reference, computation, and storage operations.

It also serves as an intermediary for data exchange with external memory. In this case, connections to DMA or other processors via SRAM are also necessary.

#### 1.2. Main Parameters

- 4x4 Matrix Mul × 2<sup>INR+1</sup> (INR is determined at implementation time), equivalent to

64 × 2<sup>INR+1</sup> multiply-accumulate units

- 4x4 Matrix Add  $\times$  2<sup>INR+1</sup> (INR is determined at implementation time), equivalent to 16  $\times$  2<sup>INR+1</sup> adders

- Throughput: Up to  $144 \times 2^{INR+1}$  operations per cycle

- Clock: Undefined (depends on the implementation process)

### 1.3. Implementation Parameters

| Parameter | Description                        | Default Value |

|-----------|------------------------------------|---------------|

| Name      |                                    |               |

| LNR       | Radix of logical SRAM depth number | 11            |

| BKR       | Radix of SRAM bank bumber          | 3             |

| CLD       | Scalar Length Radix                | 10            |

| SLR       | • SLR<=16-PNR                      | 10            |

| PNR | Processor Number Radix              | 4  |

|-----|-------------------------------------|----|

| MNR | Matrix Number Radix                 | 4  |

| IMR | Implement Multiple Radix            | 2  |

| CLR | Radix of pss channel number         | 6  |

| INR | • MNR - 2                           | 2  |

| PN  | • 1< <pnr< td=""><td>32</td></pnr<> | 32 |

| MN  | • 1< <mnr< td=""><td>32</td></mnr<> | 32 |

| IM  | • 1< <imr< td=""><td>4</td></imr<>  | 4  |

## 2. Signal Lines

### 2.1. Control Bus Interface

| Signal Name       | Ю         | Pol | Source | Description                |

|-------------------|-----------|-----|--------|----------------------------|

| cntlReq           | ı         | +   | clk    | Request signal             |

| cherceq           |           | -   | CIIC   | Evaluate cntlGnt           |

| cntlGnt           | 0         | +   | clk    | Grant signal               |

|                   |           |     |        | R/W signal                 |

| cntlRxw           |           |     | مال    | Evaluate cntlReq & cntlGnt |

| CHURXW            | l         | +   | clk    | 0: Write                   |

|                   |           |     |        | 1: Read                    |

| onth              |           |     | alle   | Address signal             |

| cntlAddr[31:0]    | I         | +   | clk    | Evaluate cntlReq & cntlGnt |

| and HIM of the la |           |     | -11-   | Write storobe signal       |

| cntlWrStrb        | l         | +   | clk    | Evaluate cntlWrAck         |

| cntlWrAck         | 0         | +   | clk    | Writ acknowledge signal    |

|                   |           |     | -11-   | Write data signal          |

| cntlWrData[31:0]  | I         | +   | clk    | Evaluate cntlWrAck         |

| - LID dChule      | IID ICI I |     | clk    | Read strobe signal         |

| cntlRdStrb I      | I         | +   |        | Evaluate cntlRdAck         |

| cntlRdAck         | 0         | +   | clk    | Read acknowledge signal    |

| IID ID 1 524 23   |           |     |        | Read data signal           |

| cntlRdData[31:0]  | 0         | +   | clk    | Sync cntlRdAck             |

| cntlIrg | 0 | _ | clk | Interrupt signal |

|---------|---|---|-----|------------------|

| CHUIIQ  | O | + | CIK | Level hold type  |

### 2.2. PSS Interface

| Signal Name   | Ю | Pol | Source | Description                                                                                                                                                                                                                                                                                         |

|---------------|---|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| iVld          | ı | +   | clk    | Pipeline start valid signal                                                                                                                                                                                                                                                                         |

| iStall        | 0 | +   | clk    | Pipeline start stall signal                                                                                                                                                                                                                                                                         |

| iCID[CLR-1:0] | I | +   | clk    | Logocal channel number                                                                                                                                                                                                                                                                              |

| iEnd[3:0]     | I | +   | clk    | Information of end of indexes                                                                                                                                                                                                                                                                       |

| iAddr[31:0]   | I | +   | clk    | <ul> <li>Address to fetch context data</li> <li>Evaluate iVld &amp; !iStall</li> <li>iAddr[31:8] and iAddr[1:0] indicates program start address</li> <li>iAddr[7:4] indicates offset of logical register bank</li> <li>iAddr[3] indicates select of volume whether iDelta or TR register</li> </ul> |

| iDelta[15:0]  | I | +   | clk    | Transfer volume  Evaluate iVld & !iStall                                                                                                                                                                                                                                                            |

| iIndex[64:0]  | I | +   | clk    | Five coordinates to specify the processing     Evaluate iVld & !iStall                                                                                                                                                                                                                              |

| oVld          | 0 | +   | clk    | Pipeline end valid signal                                                                                                                                                                                                                                                                           |

| oStall        | I | +   | clk    | Pipeline end stall signal                                                                                                                                                                                                                                                                           |

### 2.3. Memory Interface (Parameter Read Use)

| Signal Name  | Ю | Pol | Source | Description             |

|--------------|---|-----|--------|-------------------------|

| meReq        | 0 | +   | clk    | Request signal          |

| meGnt        | I | +   | clk    | Grant signal            |

| meAddr[31:0] | 0 | +   | clk    | Address signal          |

| meStrb       | 0 | +   | clk    | Read strobe signal      |

| meAck        | I | +   | clk    | Read acknowledge signal |

| meFlush      | 0 | +   | clk    | Read flush signal       |

| meData[63:0] | I | +   | clk    | Read data signal        |

### 2.4. SRAM Interface (Write Q)

| Signal Name             | Ю | Pol | Source | Description                   |

|-------------------------|---|-----|--------|-------------------------------|

| ramEQ[16*MN-1:0]        | 0 | +   | clk    | Write enable signal (MN port) |

| ramBQ[BKR-1:0]          | 0 | +   | clk    | Write bank signal             |

| ramAQ[15:MNR]           | 0 | +   | clk    | Write address signal          |

| ramDQ[16*MN*32-<br>1:0] | 0 | +   | clk    | Write data signal (MN port)   |

### 2.5. SRAM Interface (Read A/B)

| Signal Name               | Ю | Pol | Source | Description                |

|---------------------------|---|-----|--------|----------------------------|

| ramEC*                    | 0 | +   | clk    | Read enable signal         |

| ramBC*[BKR-1:0]           | 0 | +   | clk    | Read bank signal           |

| ramAC*[15:MNR]            | 0 | +   | clk    | Read address signal        |

| ramDC*[ 16*MN*3<br>2-1:0] | I | +   | clk    | Read data signal (MN port) |

<sup>\*:</sup> A/B

### 2.6. SRAM Interface (Read Write P)

| Signal Name               | Ю | Pol | Source | Description                  |

|---------------------------|---|-----|--------|------------------------------|

| ramEP[3:0]                | 0 | +   | clk    | Read enable signal (4 port)  |

| ramBP[4BKR-1:0]           | 0 | +   | clk    | Read bank signal (4 port)    |

| ramAP[4*(16-<br>MNR)-1:0] | 0 | +   | clk    | Read address signal (4 port) |

| ramMP[3:0]                | 0 | +   | clk    | Read modify signal (4 port)  |

| ramDP[16*MN*32-<br>1:0]   | I | +   | clk    | Read data signal (MN port)   |

| ramGP                     | 0 | +   | clk    | •                            |

### 2.7. Scalar Register Interface (A/B)

| Signal Name  | Ю | Pol | Source | Description        |

|--------------|---|-----|--------|--------------------|

| scEC*, scECD | 0 | +   | clk    | Read enable signal |

| 1       | SLR+PNR-<br>.:0] | 0 | + | clk | Read address signal |

|---------|------------------|---|---|-----|---------------------|

| scDC*[P | N*64-1:0]        | I | + | clk | Read data signal    |

\*: A/B

### 2.8. Utillity

| Signal Name      | Ю | Pol | Source | Description                                                                                                      |

|------------------|---|-----|--------|------------------------------------------------------------------------------------------------------------------|

| rstReq           | 0 | +   | clk    | Internal reset signal to reset the external system                                                               |

| rstAck           | ı | +   | clk    | Acknowledge of rstReq                                                                                            |

| reg_swap         | 0 | +   | clk    | Swap information for mermoy interface                                                                            |

| fReq             | ı | +   | clk    | <ul><li>1 clock early request against the miReq signal</li><li>Use to generate gate signal (for memory</li></ul> |

|                  |   |     |        | controller)                                                                                                      |

|                  |   |     |        | 1 clock early request against the meReq signal                                                                   |

| pReq             | 0 | +   | clk    | Use to generate gate signal (for memory                                                                          |

|                  |   |     |        | controller)                                                                                                      |

| gate[IM*4+1:0]   | 0 | +   | clk    | Gated clock control signal signifying condition                                                                  |

| gate[iiii 4+1.0] |   | '   | CIK    | of each internal block(expansion case is gate)                                                                   |

| gclk[IM*4+1:0]   | ı | +   | clk    | Gated clock(expansion case is gclk)                                                                              |

| clk              | I | +   | clk    | Clock                                                                                                            |

| reset            | I | +   | clk    | Synchronous reset signal                                                                                         |

| reset_n          | I | -   | clk    | Asynchronous reset                                                                                               |

## 3. Configuration and Operation Description

### 3.1. Notation

• This document uses the following notations and abbreviations for explanation.

| Symbol | Description                                         |

|--------|-----------------------------------------------------|

|        | Denotes a bit range                                 |

| [:]    | A[X:Y] represents data A with MSB at position X and |

|        | LSB at position Y                                   |

| NaN                | Represents "Not a Number" in IEEE 754 floating-<br>point format |

|--------------------|-----------------------------------------------------------------|

| Infinity           | Represents infinity in IEEE 754 floating-point format           |

| SR[n]              | 255)                                                            |

| 001.1              | Refers to the n-th 32-bit Scalar Register (n = 0 to             |

|                    | (The b designation may be omitted in some cases.)               |

| R <sub>b</sub> [n] | Vector Register (b = 0 to $2^{BKR}$ - 1, n = 0 to 15).          |

|                    | Refers to the 32-bit register number n in bank b of the         |

### 3.2. System Overview

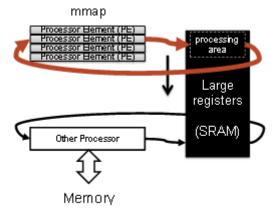

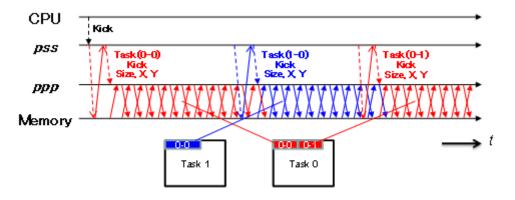

• As shown in Figure 1, *mmap* is a processor in which 2<sup>INR+1</sup> processor elements sequentially scan and process the register file (SRAM).

Figure 1 *mmap* system⊎

- It is not directly connected to memory; instead, data exchange is performed through the register file. Another processor (for example, our company's processors such as *dmap* or *pp*) supplies and retrieves data from the register file.

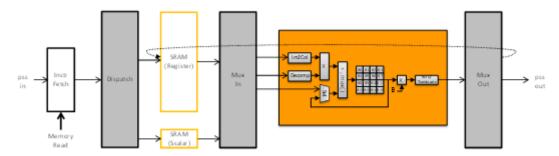

- The figure represents the overall block structure. The processor is driven by pss and continues computation until the program finishes. The architecture is designed such that increasing the number of pipeline stages does not affect performance, and the register file is assumed to be implemented in SRAM

Figure 3 Block Diagram⊎

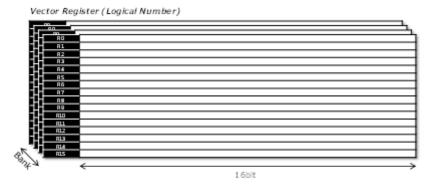

• The SRAM (register file) consists of 16 16-bit vector registers per unit, organized into 2<sup>LNR+1</sup> sets × 2<sup>BKR</sup> banks. The value 2<sup>LNR+1</sup> corresponds to the maximum number of logical processors. When another processor accesses it in 32-bit mode, even-numbered logical processor IDs map to the lower 16 bits, and odd-numbered ones to the upper 16 bits.

Figure 4 Register File⊎

- Generally, R[0] to R[15] in the register file store 4×4 matrix data, and the results of

matrix multiplication and addition between banks are stored into the designated bank. If

the banks are configured exclusively, the original data can be preserved.

- By utilizing the im2col function and organizing the register file data in a specialized layout, the processor supports multiplication, accumulation, and min/max operations on arbitrary matrices up to 256 × 256 in size.

- Using im2col, arbitrary numbers of input and output channels can be defined. Channel data

is expanded into the register file according to the step values specified in the command

list.

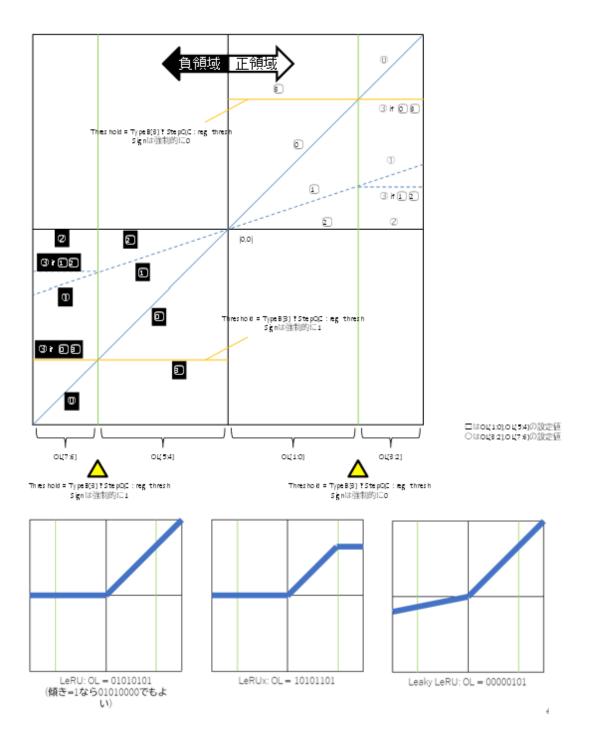

- Accumulation can be performed using either 16-bit half-precision floating-point or 8-bit floating-point formats. Addition is always performed using 16-bit half-precision floating-point. At the final stage, transposition and application of an activation function for deep learning are supported. The activation function can be defined using up to three-piece linear segments, allowing implementation of ReLU or Leaky ReLU.

- In place of the register file, each logical processor can also reference shared scalar

**registers**. These are used for common coefficients or constants. **Scalar registers** are also shared with other processors and can be accessed bidirectionally.

#### 3.3. Drive Interface (Initiator)

The pss sends XYZW indices to the Initiator of the P-Cube (PX, PY, PZ, PW). The

configuration for pss (such as processing units) is pre-arranged in memory. The pss

manages multiple configurations (N in number, depending on implementation) using time

division, and after scheduling, it drives the mmap.

Figure 5 Resource Sharing using pss□

The Initiator reads from memory using the start address of the command sent by pss and sets up the pipeline. It repeats processing based on the amount indicated by iDelta in pss. If iAddr[4] is '0', the processing amount is iDelta (1D mode).

If iAddr[4] is '1', it interprets iDelta as two dimensions: ΔX = iDelta[7:0], ΔY = iDelta[15:8], and performs 2D processing. In the latter case, it does not use the index indicated by pss, making it effective for processing in small units.

### 3.4. Fragmentation Considerations

• In general, fragmentation poses no issues; however, when using the *im2col* function, fragmentation is not allowed.

#### 3.5. Instruction Start and End

The *mmap* performs processing for the amount indicated by iDelta from *pss* using a single instruction.

To use it repeatedly, pss settings must be configured accordingly.

### 3.6. Floating-Point Operations

- Multiply-accumulate floating-point operations support both IEEE 754 half-precision (16-bit) and 8-bit formats.

- Addition floating-point operations are all performed using IEEE 754 half-precision (16-bit) format.

- Depending on the computation result, NaN or Infinity may be generated. No exception interrupts are triggered. However, the overflow flag may change, and if necessary, the system can assert an interrupt accordingly.

A + B ←

| A←<br>B←  | 0←3             | A∈            | Infinity₽      | NaN⊴ |

|-----------|-----------------|---------------|----------------|------|

| 0←□       | 0←              | A∈□           | Infinity∈      | NaN∈ |

| Bċ□       | B, -B <b></b> ← | A + B, A - B∈ | Infinity⊲      | NaN∈ |

| Infinity⊲ | Infinity⊲       | Infinity∈     | Infinity, NaN⊲ | NaN∈ |

| NaN⊲      | NaN∈            | NaN∈          | NaN∂           | NaN∈ |

A \* B⊢

| A←<br>B←  | 0€   | A∈        | Infinity∉ | NaN∈ |

|-----------|------|-----------|-----------|------|

| 0←        | 0←   | 0←        | NaN∈      | NaN∈ |

| B⊲        | 0←   | A * B⊲    | Infinity∉ | NaN∈ |

| Infinity₽ | NaN∂ | Infinity₽ | Infinity₫ | NaN∈ |

| NaN∈      | NaN∈ | NaN∈      | NaN∈      | NaN∂ |

#### 3.7. im2col Matrix Operations

- By arranging the data in the register file in a specialized layout and setting TypeP[0] in the command list to "1", it becomes possible to perform arbitrary matrix multiplication, accumulation, and min/max operations using the im2col function, supporting matrix sizes up to 256 × 256.

- In im2col matrix operations, arbitrary numbers of input channels (C) and output channels

(M) can be defined. Channel data is expanded into the register file according to Step parameters specified in the command list.

### 3.8. Standard Matrix Operations

- Supports execution of 4 × 4 matrix AxP + B operations. Set TypeP[0] to "0".

- The number of 4 × 4 matrices to be processed is defined by pss size (W0).

- For FP16 data format, up to 8 simultaneous 4 × 4 matrix operations are executed.

For FP8, up to 16 simultaneous 4 × 4 matrix operations are executed.

#### 3.9. Hadamard Matrix Operations

- Supports execution of 4 × 4 Hadamard matrix operations. Set TypeP[1] to "1".

- The number of 4 × 4 matrices to be processed is defined by pss size (W0).

- For FP16 data format, up to 8 simultaneous 4 × 4 Hadamard operations are executed.

For FP8, up to 16 simultaneous 4 × 4 Hadamard operations are executed.

### 3.10. Min/Max Function

By configuring Min/Max settings in im2col matrix operations, it is possible to implement

MinPooling/MaxPooling functionalities.

### 3.11. Register File Structure

• The **SRAM** (register file) is composed of 16 **16-bit vector registers** per unit, organized into 2<sup>LNR+1</sup> sets × 2<sup>BKR</sup> banks.

#### 3.12. Parallel Circuits

- The multiply-accumulate units used for matrix operations are structured in parallel as follows:

- o 2 parallel units for FP16 support

- o 4 parallel units for FP8 support

### 3.13. Computational Error

This section is under preparation.

### 4. Control Register Description

### 4.1. Overview

- Control registers are accessed via the control bus. Unlike R[n], these registers are shared settings across the processor, and include scalar registers.

- In the detailed register descriptions, the following symbols are used to indicate access types:

- o R Read Only (writes have no effect)

- o R/W Read / Write

- o R/WC Read / Write with Clear on write

- Do not access registers marked as Reserved. When writing to reserved fields, set the value to '0'.

- In address and data notations, 'x' indicates don't care.

### 4.2. Definition

| Address   | Register Name | Description                           |

|-----------|---------------|---------------------------------------|

| 0000_0000 | Reset         | Reset control                         |

| 0000_0004 | System        | Gated Clock Control, Data Bus Control |

| 0000_0008 | _             | Reserved                              |

| 0000_000c | -             | Reserved                              |

| 0000_0010 | Control       | Master control                        |

| 0000_0014 | Val           | Coefficient Setting                   |

| 0000_0018 | ConstAB       | Coefficient Setting                   |

| 0000_001c | _             | Reserved                              |

| 0000_0020 | Select        |                                       |

| 0000_0024 | _             | Reserved                              |

| 0000_0028 | _             | Reserved                              |

| 0000_002c | _             | Reserved                              |

| 0000_0030 | -             | Reserved                              |

| 0000_0034 | _             | Reserved                              |

| 0000_0038 | -             | Reserved                              |

| 0000_003c | _             | Reserved                              |

| 0000_0040 | MonitorXY   | Active Index XY |

|-----------|-------------|-----------------|

| 0000_0044 | MonitorZW   | Active Index ZW |

| 0000_0048 | MonitorST   | Active Index ST |

| 0000_004c | MonitorID   | Active Index ID |

| 0000_0050 | BreakXY     | Break index XY  |

| 0000_0054 | BreakZW     | Break index ZW  |

| 0000_0058 | BreakST     | Break index ST  |

| 0000_005c | BreakID     | Break index ID  |

| 0000_0060 | BCondition0 |                 |

| 0000_0064 | BCondition1 |                 |

| 0000_0068 | _           | Reserved        |

| 0000_006c | _           | Reserved        |

### 4.3. Details

### 4.3.1.1. Reset Register

[Address: 0x0000\_0000]

| Name  | I ype | Default | Description                                                |

|-------|-------|---------|------------------------------------------------------------|

| Reset | R/W   | 0       | Synchronous Reset                                          |

|       |       |         | After being set to '1', the internal reset state is        |

|       |       |         | triggered and then automatically cleared.                  |

|       |       |         | Unlike the reset_n signal, the contents of other registers |

|       |       |         | are preserved.                                             |

### 4.3.1.2. System Register

| Name | Type | Default | Description                                 |

|------|------|---------|---------------------------------------------|

| Swap | R/W  | 0       | Configures the final byte swap with memory. |

The behavior follows the same specification as instruction-based swapping (refer to the 2D access mode of memory instructions).

For write operations, the swap specified in the instruction is applied after this swap.

For read operations, the swap specified in the instruction is applied after this swap.

GateOff R/W 0 Gated Clock Off Mode

When set to '1', all bits of the **gate** signal are forcibly fixed to '1'.

### 4.3.1.3. Control Register

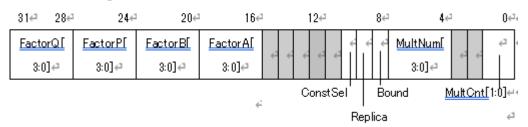

[Address: 0x0000\_0010] ←

| Name         | Туре | Default | Description                                                                                                  |

|--------------|------|---------|--------------------------------------------------------------------------------------------------------------|

| FactorQ[3:0] | R/W  | 0       |                                                                                                              |

| FactorP[3:0] | R/W  | 0       |                                                                                                              |

| FactorB[3:0] | R/W  | 0       |                                                                                                              |

| FactorA[3:0] | R/W  | 0       |                                                                                                              |

| ConstSel     | R/W  | 0       |                                                                                                              |

|              |      |         | ConstSel         Use           0         StepPM, StepQC           reg_constAB         /reg_slope, reg_thresh |

| Replica  | R/W     | 0 |

|----------|---------|---|

| rtepiica | 1 1/ 44 | U |

| Bound        | R/W | U |                                                       |

|--------------|-----|---|-------------------------------------------------------|

| MultNum[3:0] | R/W | 0 |                                                       |

| MultCnt[1:0] | R/W | 0 | •MAX represents the maximum parallelism of Channel M. |

Automatically selected based on TypeP

| MultCntl | M並列度                |

|----------|---------------------|

| 0        | Auto (1,2,4,,, MAX) |

| 1        | Auto (1 or MAX)     |

| 2        | Fixed (MultNum)     |

| 3        | Reserved            |

### 4.3.1.4. Value Register

[Address: 0x0000\_0014]⊬

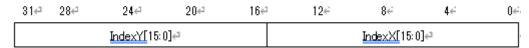

| 31₽ | 28₽                | 24← | 20₽ | 16∉ | 12€ | 8€                 | 4← | 0 ← - |

|-----|--------------------|-----|-----|-----|-----|--------------------|----|-------|

|     | <u>Th[</u> 15:0]₄⊐ |     |     |     |     | <u>Slope[</u> 15:0 | ]₽ | 4     |

| Name  | Туре | Default | Description                                               |

|-------|------|---------|-----------------------------------------------------------|

| Th    | R/W  | 0       | •Threshold (Th) applied to the LUT used for the final     |

|       |      |         | output value                                              |

| Slope | R/W  | 0       | •Slope applied to the LUT used for the final output value |

### 4.3.1.5. ConstAB Register

[Address: 0x0000\_0018]⊬

| 31↩ | 28₽                    | 24← | 20↩ | 16↩ | 12∉ | 8←3               | 4←   | 0←7- |

|-----|------------------------|-----|-----|-----|-----|-------------------|------|------|

|     | <u>Const B[</u> 15:0]← |     |     |     |     | <u>ConstA</u> [15 | :0]₽ |      |

| Name   | Type | Default | Description                  |

|--------|------|---------|------------------------------|

| ConstB | R/W  | 0       | •Fixed value to be set for B |

| ConstA | R/W  | 0       | •Fixed value to be set for A |

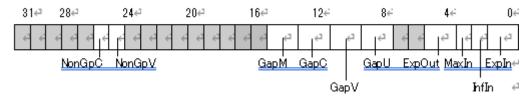

### 4.3.1.6. Select Register

### [Address: 0x0000\_0020]

| Name   | Type | Default | Description                                    |

|--------|------|---------|------------------------------------------------|

| NonGpC | R/W  | 0       | NonGp SRAM Group 0 if Step=0 force to 0 1 none |

| NonGpV | R/W  | 0       |                                                |

| GapM   | R/W  | 0       | •                                              |

| GapC   | R/W  | 0       | •                                              |

| GapV   | R/W  | 0       | •                                              |

| GapU   | R/W  | 0       | •                                              |

| ExpOut | R/W  | 0       | • Format selection for FP8 output    ExpOut    |

| MaxIn  | R/W  | 0       | Maxin Exp Max 0 1f 1 1e                        |

| InfIn  | R/W  | 0       | Infin Max(7fff/ffff) x Zero 0 7ffff/ffff 1 0   |

ExpIn R/W 0 •Format selection for FP8 output

| Expln | fp8 Input |

|-------|-----------|

| 0     | 1-5-2     |

| 1     | 1-4-3     |

| 2     | 1-3-4     |

| 3     | Reserved  |

### 4.3.1.7. Monitor Register

[Address: 0x0000\_0040]

| Name   | Туре | Default | Description                               |

|--------|------|---------|-------------------------------------------|

| IndexY | R    | 0       | Indicates the currently executing index Y |

| IndexX | R    | 0       | Indicates the currently executing index X |

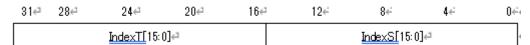

### 4.3.1.8. MonitorZW Register

[Address: 0x0000\_0044]↔

| 31←                   | 28₽ | 24← | 20↩ | 16₽ | 12€ | 8≓                  | 4€  | 0€ |

|-----------------------|-----|-----|-----|-----|-----|---------------------|-----|----|

| <u>IndexW[</u> 15:0]↵ |     |     |     |     |     | <u>IndexZ[</u> 15:0 | ],⊒ |    |

| Name   | Туре | Default | Description                               |

|--------|------|---------|-------------------------------------------|

| IndexW | R    | 0       | Indicates the currently executing index W |

| IndexZ | R    | 0       | Indicates the currently executing index Z |

### 4.3.1.9. MonitorST Register

[Address: 0x0000\_0048]

| Name   | Type | Default | Description                               |

|--------|------|---------|-------------------------------------------|

| IndexT | R    | 0       | Indicates the currently executing index T |

| IndexS | R    | 0       | Indicates the currently executing index S |

### 4.3.1.10. MonitorID Register

[Address: 0x0000\_004c] <

e I

| Name                 | Type   | Default | Description                                |

|----------------------|--------|---------|--------------------------------------------|

| ID                   | R      | 0       | Indicates the currently executing index ID |

| 4.3.1.11. BreakXY Re | gister |         |                                            |

[Address: 0x0000\_0050]

| 31₽ | 28₽ | 24←                 | 20∉ | 16↩ | 12€ | 8⋵                  | 4← | 0 ← |

|-----|-----|---------------------|-----|-----|-----|---------------------|----|-----|

|     |     | <u>IndexY[</u> 15:1 | 0]↩ |     |     | <u>IndexX[</u> 15:0 | ]∉ | 4   |

| Name | Type | Default | Description                                         |

|------|------|---------|-----------------------------------------------------|

| Y    | R/W  | 0       | Specifies the break index Y.                        |

|      |      |         | Processing will halt before this index is executed. |

|      |      |         | Setting the value to '0' cancels the break.         |

| Χ    | R/W  | 0       | Specifies the break index X. Performs the same      |

|      |      |         | operation as index Y.                               |

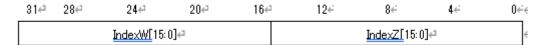

### 4.3.1.12. BreakZW Register

[Address: 0x0000\_0054]⊬

| Name | Type | Default | Description                               |      |

|------|------|---------|-------------------------------------------|------|

| W    | R/W  | 0       | Specifies the break index W. Performs the | same |

|      |      |         | operation as index Y.                     |      |

| Z    | R/W  | 0       | Specifies the break index Z. Performs the | same |

|      |      |         | operation as index Y                      |      |

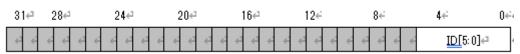

### 4.3.1.13. BreakST Register

[Address: 0x0000\_0058]

| 31₽                   | 28₽ | 24← | 20₽ | 16↩ | 12€ | 8≓                  | 4←  | 0 ← |

|-----------------------|-----|-----|-----|-----|-----|---------------------|-----|-----|

| <u>IndexT[</u> 15:0]↩ |     |     |     |     |     | <u>IndexS[</u> 15:0 | ٦[( | 4   |

| Name   | Type | Default | Description | n     |        |       |      |          |     |      |

|--------|------|---------|-------------|-------|--------|-------|------|----------|-----|------|

| IndexT | R/W  | 0       | Specifies   | the   | break  | index | T.P  | erforms  | the | same |

|        |      |         | operation   | as in | dex Y. |       |      |          |     |      |

| IndexS | R/W  | 0       | Specifies   | the   | break  | index | S. F | Performs | the | same |

|        |      |         | operation   | as in | dex Y. |       |      |          |     |      |

### 4.3.1.14. BreakID Register

### 5. Command List Description

#### 5.1. Overview

- The command list has its starting address specified by the address value output from pss.

After MMAP is activated, it retrieves the command list and stores it into internal registers.

- The command list is independently managed at each stage within the pipeline. As a result, even during pipeline operation, it is possible to hold different command lists and drive the executable stages accordingly. Therefore, synchronization commands are not required.

- For reserved registers and fields, set the value to '0'.

- The addresses shown are relative to the address value output from pss.

### 5.2. Definition

| Address  | Command Name | Description                              |  |  |  |  |  |  |  |

|----------|--------------|------------------------------------------|--|--|--|--|--|--|--|

| 00       | Cntl         | Control Command                          |  |  |  |  |  |  |  |

| 04       | Format       | Data Format Setting                      |  |  |  |  |  |  |  |

| 08       | Offset       | Coordinate Offset / Vector Register Bank |  |  |  |  |  |  |  |

| 08       | Offset       | Configuration                            |  |  |  |  |  |  |  |

| 0C       | Gap          | Gap Configuration per Channel            |  |  |  |  |  |  |  |

| 10       | Size         | Size Configuration per Channel           |  |  |  |  |  |  |  |

| 14       | Size         | Size Configuration per Channel           |  |  |  |  |  |  |  |

| 18       | StepO        | Step Configuration per Channel           |  |  |  |  |  |  |  |

| 1C StepO |              | Step Configuration per Channel           |  |  |  |  |  |  |  |

| 20       | StepA        | Step Configuration per Channel           |  |  |  |  |  |  |  |

| 24       | StepA        | Step Configuration per Channel           |  |  |  |  |  |  |  |

| 28       | StepB        | Step Configuration per Channel           |  |  |  |  |  |  |  |

| 2C       | StepB        | Step Configuration per Channel           |  |  |  |  |  |  |  |

| 30       | StepP        | Step Configuration per Channel           |  |  |  |  |  |  |  |

| 34       | StepP        | Step Configuration per Channel           |  |  |  |  |  |  |  |

| 38       | StepQ        | Step Configuration per Channel           |  |  |  |  |  |  |  |

| 3с       | StepQ        | Step Configuration per Channel           |  |  |  |  |  |  |  |

### 5.3. Details

### 5.3.1.1 Cntl Command

The command details are described below.

[Address: 0x0000\_0000]

| 31₽   | 28∉ | 24€                  | 20↩  | 16€ | 12€ | 8←  | 4 <i>←</i> | 0← |

|-------|-----|----------------------|------|-----|-----|-----|------------|----|

| Util₽ |     | <u>OL(</u> Output Lu | ut)∉ | KV₽ |     | KU⊄ |            |    |

Name Size Description

Util 4 •[0]: U, [1]: V Sampling Point Configuration

| Util[0][1] | Sampling Point U/V |

|------------|--------------------|

| 0          | +0                 |

| 1          | +1                 |

| Util[2] | Gap        |

|---------|------------|

| 0       | Zero Write |

| 1       | Mask Write |

•Parallel Circuit Usage Configuration

Setting to "1" disables the use of parallel circuits.

| Util[3] | Multi Force One |

|---------|-----------------|

| 0       | Auto Set        |

| 1       | Force 1         |

Next address when the bank address reaches the end of the bank

| Util[4]-[7] | Bank Bound [A][B][P][Q] |  |  |

|-------------|-------------------------|--|--|

| 0           | Carry                   |  |  |

| 1           | Ring                    |  |  |

OL 8 LUT selection applied to the final output value

- For each of the four regions into which the output value is divided Select from the four output processing options shown in the table below.

- •The boundaries of the regions are configured using Th in

- 4.3.1.4 Value Register

$$OL[5:4]$$

-Th  $\sim 0$

$$OL[1:0] 0 \sim +Th$$

| Op | Output                 |  |  |  |

|----|------------------------|--|--|--|

| 0  | f(x)                   |  |  |  |

| 1  | f(x)*slope             |  |  |  |

| 2  | 0                      |  |  |  |

| 2  | (sign?-thresh: thresh) |  |  |  |

| 3  | *(1 or slope)          |  |  |  |

KV 8 Set the kernel size (vertical direction) to the value of **size 1**.

KU 8 Set the kernel size (horizontal direction) to the value of **size 1**.

### 5.3.1.2 Format Command

[Address: 0x0000\_0004]

| 31₽  | 28∉ | 24€      | 20€    | 16⊖             | 12€    | 8€     | 4+     | 0←     | i, |

|------|-----|----------|--------|-----------------|--------|--------|--------|--------|----|

| Form | nQ∉ | For mP ← | FormB⊄ | For mA <i>←</i> | TypeQ∉ | TypeP∉ | TypeB₽ | TypeA⋳ |    |

-7

FormQ

4 •Output Q value format setting

| FormQ[3][2] | Compress U/V |

|-------------|--------------|

| 0           | -            |

| 1           | On           |

| Form*[1:0] | Data Type |

|------------|-----------|

| 0          | fp16      |

| 1          | fp8       |

| 2          |           |

| 3          |           |

FormP

4 • Input P value format setting

| Form*[1:0] | Data Type |

|------------|-----------|

| 0          | fp16      |

| 1          | fp8       |

| 2          |           |

| 3          |           |

${\sf FormB}$

4 •Input B value format setting

| Form*[1:0] | Data Type |

|------------|-----------|

| 0          | fp16      |

| 1          | fp8       |

| 2          |           |

| 3          |           |

Coefficient Expansion Direction Setting

Automatically set to "1" during im2col. Automatic behavior can be disabled by setting reg\_autoRepOff = 1.

| FormB[3:2] | Coef Arrange on im2col |

|------------|------------------------|

| 0          | U Replica              |

| 1          | M Replica              |

| 2          | M+ Replica             |

| 3          | Reserved               |

$\mathsf{Form}\mathsf{A}$

4 Input A value format setting

| ĺ | Form*[1:0] | Data Type |

|---|------------|-----------|

|   | 0          | fp16      |

| ĺ | 1          | fp8       |

|   | 2          | fp4       |

| 1 | 3          | fn2       |

Coefficient Expansion Direction Setting

| FormA[3:2] | Coef Arrange on im2col |

|------------|------------------------|

| 0          | U Replica              |

| 1          | M Replica              |

| 2          | Reserved               |

| 3          | Reserved               |

TypeQ

4

• Calculation Setting for Output Q

| TypeQ[0] | Translocate |

|----------|-------------|

| 0        | -           |

| 1        | On          |

| TypeQ[1] | Flat (notwiddle) |

|----------|------------------|

| 0        | -                |

| 1        | On               |

| TypeQ[3:2] | new | not new |

|------------|-----|---------|

| 0          | В   | В       |

| 1          | Acc | В       |

| 2          | В   | Acc     |

| 3          | Acc | Acc     |

TypeP 4 • Calculation Setting for Input P

| Турей | P[0] | Property |

|-------|------|----------|

| 0     |      | Normal   |

| 1     |      | lm2Col   |

| TypeP[1] | Product  |

|----------|----------|

| 0        | Normal   |

| 1        | Hadamard |

| TypeP[3:2] | Merge  |  |  |  |  |  |

|------------|--------|--|--|--|--|--|

| 0          | Normal |  |  |  |  |  |

| 1          | 1      |  |  |  |  |  |

| 2          | Min    |  |  |  |  |  |

| 3          | Max    |  |  |  |  |  |

TypeB 4 • Configuration of storage location or fixed value for input B

| TypeAB[2:0] | Operand           |  |  |  |

|-------------|-------------------|--|--|--|

| 0           | RegisterVec(addr) |  |  |  |

| 1           | RegisterSel(addr) |  |  |  |

| 2           | ScalarVec(addr)   |  |  |  |

| 3           | ScalarSel(addr)   |  |  |  |

| 4           | Zero              |  |  |  |

| 5           | One               |  |  |  |

| 6           | Identity          |  |  |  |

| 7           | Const             |  |  |  |

| TypeAB[3] | Address Shrink |

|-----------|----------------|

| 0         | -              |

| 1         | On             |

TypeA 4 •Input B Value: Storage Location or Fixed Value Configuration

Same as TypeB

### 5.3.1.3 Offset Command

[Address: 0x0000\_0008]

| 31₽  |   |       |       |       | 124    | •      | 4∻     |          |

|------|---|-------|-------|-------|--------|--------|--------|----------|

| OffM | 4 | OffC∉ | OffV∉ | OffU∉ | BankQ∉ | BankP∉ | BankB∉ | BankA∉ ∉ |

| Name   | Size | Description                                |  |

|--------|------|--------------------------------------------|--|

| OffM 4 |      | Processing Start Coordinate Offset Setting |  |

Negative values are represented in two's complement.

Negative values are represented in two's complement

The valid range is -8 to 7.

| OffC | 4 | Processing Start Coordinate Offset Setting          |

|------|---|-----------------------------------------------------|

|      |   | Negative values are represented in two's complement |

|      |   | format.                                             |

|      |   | The valid range is $-8$ to 7.                       |

| OffV | 4 | Processing Start Coordinate Offset Setting          |

The valid range is -8 to 7.

format.

OffU 4 Processing Start Coordinate Offset Setting

Negative values are represented in two's complement format.

The valid range is -8 to 7.

BankQ 4 Register File Bank Configuration

BankP 4 Register File Bank Configuration

BankB 4 Register File Bank Configuration

BankA 4 Register File Bank Configuration

### 5.3.1.4. Gap Command

[Address: 0x0000\_000c]

| 31₽ | 28∉ | 24€ | 20∉ | 16↩ | 12€ | 8€ | 4€             | 0€4 |

|-----|-----|-----|-----|-----|-----|----|----------------|-----|

|     | M←  |     | C∉  |     | V⊎  |    | Π <sup>ć</sup> |     |

| Name | Size | Description                                   |

|------|------|-----------------------------------------------|

| M    | 8    | • Gap value set for the output channel        |

| С    | 8    | •Gap value set for the intput channel         |

| ٧    | 8    | • Gap value set in the vertical (V) direction |

| U    | 8    | •Gap value set in the vertical (U) direction  |

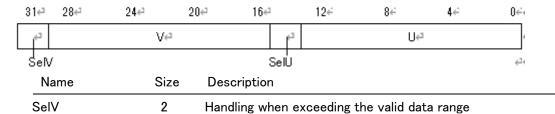

### 5.3.1.5. Size Command

[Address: 0x0000\_0010] ←

|   | ize.Sel       | ·у  | PELIS | ٠٤] |

|---|---------------|-----|-------|-----|

| 3 | Norm          | Min | Max   |     |

| 0 | -             | -   | -     | -   |

| 1 | under border  | 0   | +PM   | -   |

| 2 | over border   | 0   | -     | -PM |

| 3 | out of border | 0   | +PM   | -PM |

|   |               |     |       |     |

PM: Possible Max (0x7bff)

V 14 Matrix size of input data (vertical direction)

Set the value of size n minus 1.

SelU 2 Same as SelV

U 14 Matrix size of input data (Horizontal direction)

Set the value of size n minus 1.

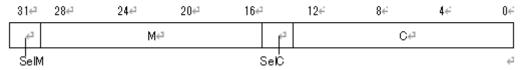

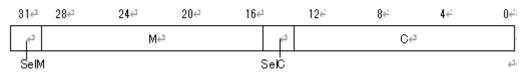

### 5.3.1.6. Size Command

[Address: 0x0000\_0014]↔

| Name | Size | Description                                            |

|------|------|--------------------------------------------------------|

| SelM | 2    | Same as SelV                                           |

| M    | 14   | Output channel size  Set the value of size n minus 1.。 |

SelC 2 Same as SelV

Set the value of size n minus 1.

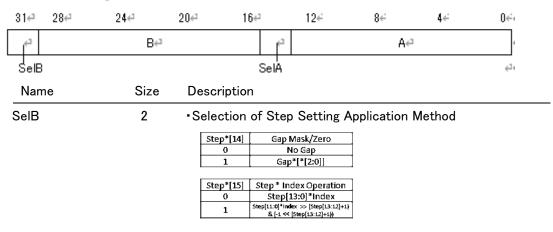

### 5.3.1.7. StepO Command

[Address: 0x0000\_0018]

B 14 Base address of input B within the bank

SelA 2 same as SelB

A Base address of input A within the bank

### 5.3.1.8. StepO Command

[Address: 0x0000\_001 c]↔

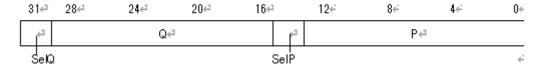

| Name | Size | Description                              |

|------|------|------------------------------------------|

| SelQ | 2    | Same as SelB in StepO                    |

| Q    | 14   | Base address of output Q within the bank |

| SelP | 2    | Same as SelB in StepO                    |

### 5.3.1.9. StepA Command

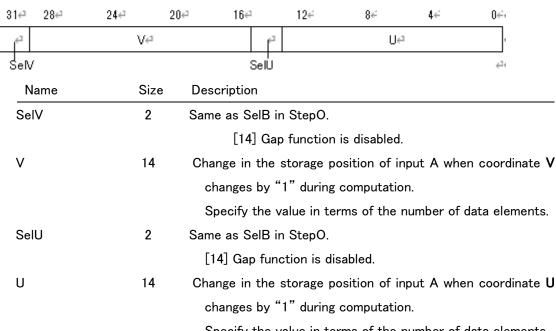

[Address: 0x0000\_0020]

Specify the value in terms of the number of data elements.

### 5.3.1.10. StepA Command

[Address: 0x0000\_0024]↔

| 31 ← 28 ← | 24∉ 20∉ | 16€              | 12€          | 8≓            | 4€         | 0€               |

|-----------|---------|------------------|--------------|---------------|------------|------------------|

| تم        | M⇔      | ٦                |              | C#            | 3          |                  |

| SelM      |         | Selc             |              |               |            | 4                |

| Name      | Size    | Description      |              |               |            |                  |

| SelM      | 2       | Same as SelB     | in StepO.    |               |            |                  |

|           |         | [14] Gap fun     | ction is dis | sabled.       |            |                  |

| М         | 14      | •Change in the   | storage po   | osition of in | put A when | output channel   |

|           |         | <b>M</b> changes | by "1" du    | ring compu    | tation.    |                  |

|           |         | Specify the      | value in t   | erms of the   | number of  | f data elements. |

| SelC      | 2       | Same as SelB     | in StepO.    |               |            |                  |

|           |         | [14] Gap fun     | ction is dis | sabled.       |            |                  |

- C C change in the storage position of input A when input channel

C changes by "1" during computation.

- Specify the value in terms of the number of data elements.

### 5.3.1.11. StepB Command

| V | 14 | Change in the storage position of input B when coordinate ${f V}$ |

|---|----|-------------------------------------------------------------------|

|   |    | changes by "1" during computation.                                |

Specify the value in terms of the number of data elements.

| SelU 2 | 2 | Same as SelB in StepO. [14] Gap function is disabled. |

|--------|---|-------------------------------------------------------|

|--------|---|-------------------------------------------------------|

14 Change in the storage position of input B when coordinate **U** changes by "1" during computation.

Specify the value in terms of the number of data elements.

### 5.3.1.12. StepB Command

U

[Address: 0x0000\_002c]

| Name | Size | Description                                                   |

|------|------|---------------------------------------------------------------|

| SelM | 2    | Same as SelB in StepO. [14] Gap function is disabled.         |

| М    | 14   | Change in the storage position of input A when output channel |

|      |      | M changes by "1" during computation.                          |

|      |      | Specify the value in terms of the number of data elements.    |

| SelC | 2    | Same as SelB in StepO. [14] Gap function is disabled.         |

| С    | 14   | Change in the storage position of input A when input channel  |

|      |      | C changes by "1" during computation.                          |

|      |      | Specify the value in terms of the number of data elements.    |

### 5.3.1.13. StepP Command

[Address: 0x0000\_0030]

Specify the value in terms of the number of data elements.

### 5.3.1.14. StepP Command

[Address: 0x0000\_0034]

| Name | Size | Description                                                         |

|------|------|---------------------------------------------------------------------|

| SelM | 2    | Same as SelB in StepO. [14] Gap function is disabled.               |

| М    | 14   | Change in the storage position of input ${f P}$ when output channel |

|      |      | <b>M</b> changes by "1" during computation.                         |

|      |      | Specify the value in terms of the number of data elements.          |

|      |      | Normally set to <b>0</b> .                                          |

| SelC | 2    | Same as SelB in StepO. [14] Gap function is disabled.               |

| С    | 14   | Change in the storage position of input ${f P}$ when input channel  |

|      |      | C changes by "1" during computation.                                |

|      |      | Specify the value in terms of the number of data elements.          |

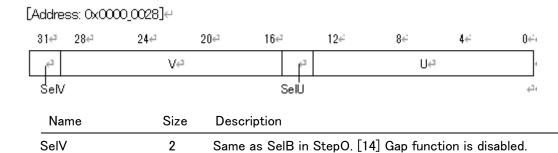

### 5.3.1.15. StepQ Command

[Address: 0x0000\_0038]

| Name | Size | Description                                                              |

|------|------|--------------------------------------------------------------------------|

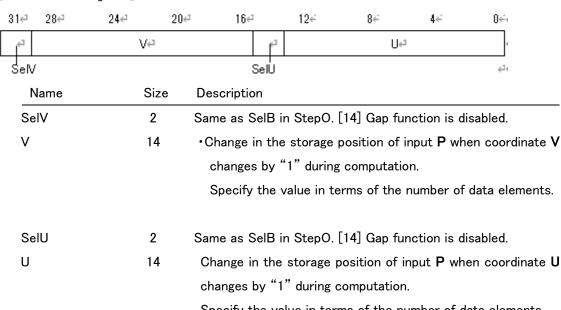

| SelV | 2    | Same as SelB in StepO. [14] Gap function is disabled.                    |

| V    | 14   | Change in the storage position of output ${f Q}$ when coordinate ${f V}$ |

|      |      | changes by "1" during computation.                                       |

|      |      | Specify the value in terms of the number of data elements.               |

| SelU | 2    | Same as SelB in StepO. [14] Gap function is disabled.                    |

| U    | 14   | Change in the storage position of output ${f Q}$ when coordinate ${f U}$ |

|      |      | changes by "1" during computation.                                       |

Specify the value in terms of the number of data elements.

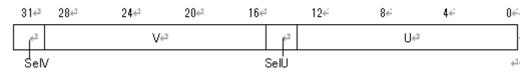

### 5.3.1.16. StepQ Command

[Address: 0x0000\_003c]

| Name | Size | Description                                                         |

|------|------|---------------------------------------------------------------------|

| SelM | 2    | Same as SelB in StepO. [14] Gap function is disabled                |

| M    | 14   | Change in the storage position of output ${f Q}$ when output        |

|      |      | channel <b>M</b> changes by "1" during computation.                 |

|      |      | Specify the value in terms of the number of data elements.          |

| SelC | 2    | Same as SelB in StepO. [14] Gap function is disabled                |

| С    | 14   | Change in the storage position of output ${f Q}$ when input channel |

|      |      | C changes by "1" during computation.                                |

|      |      | Specify the value in terms of the number of data elements.          |

|      |      | Normally set to <b>0</b> .                                          |

## 6. Application Note

### 6.1. Example Implementation

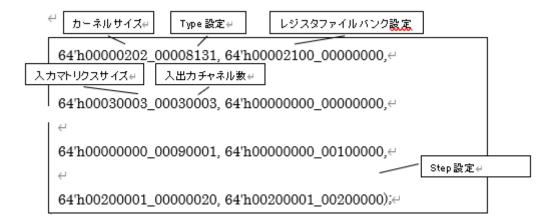

#### 6.1.1. conv2d (im2col)

This is an example command list (CL) used for conv2D(im2col) processing.

○ Input data matrix size: 4 × 4

o Number of input channels: 4

Number of output channels: 3

### 6.1.2. LUT Applied to the Final Output Value

• The relationship between each setting value and the output is shown in the diagram below.