IPEソリューション

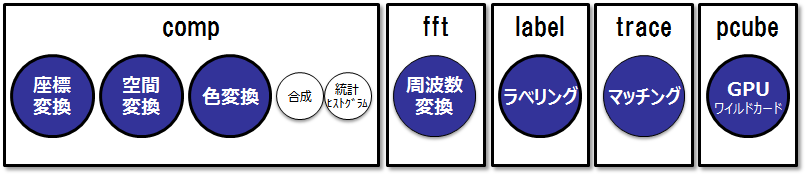

IPEの構成要素

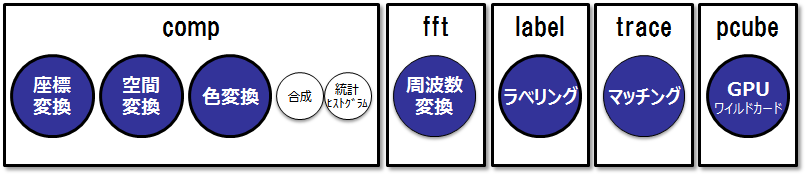

- IPEは基本IP(comp)と拡張IP(fft, label, trace)および独自GPU(P-Cube)で構成されています。

- 一般画像処理に加えて、距離測定や各種認識処理などのインテリジェント応用もアクセラレート可能です。

- 各IPはマイクロパケット処理され、異なるパラメータを与えることで、複数の異なる機能部品として制御されます。

- 基本3つの部品で一般的な画像処理に対応します。これらは1つのIP(comp)にパッケージされています。

- 拡張3つの部品でその他の画像処理に対応します。それぞれIP(fft, label, trace)として存在します。

- 基本IPと拡張IPでカバーできない画像処理は、GPU(P-Cube)で処理します。

- システムの要望により、IPを2重化したり、ユーザー回路を組み込んだりすることも可能です。

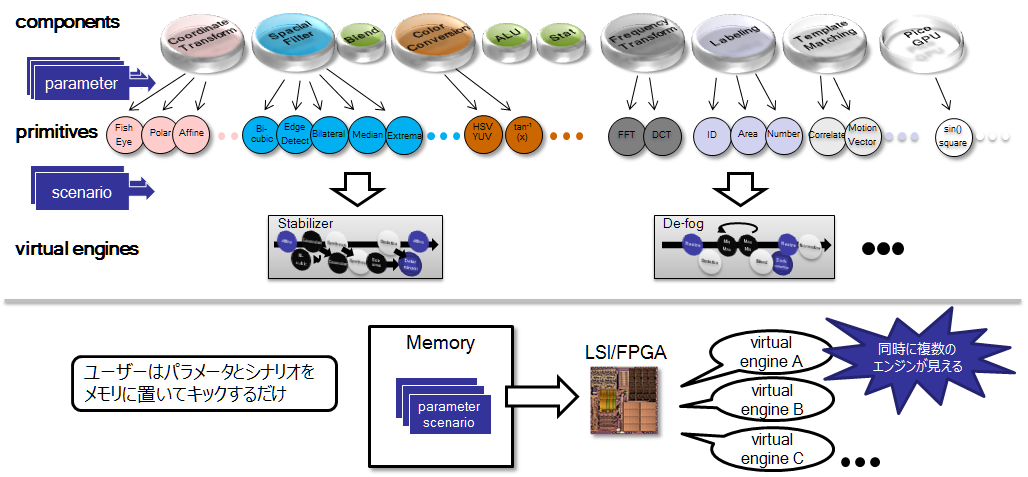

柔らかい画像処理エンジン

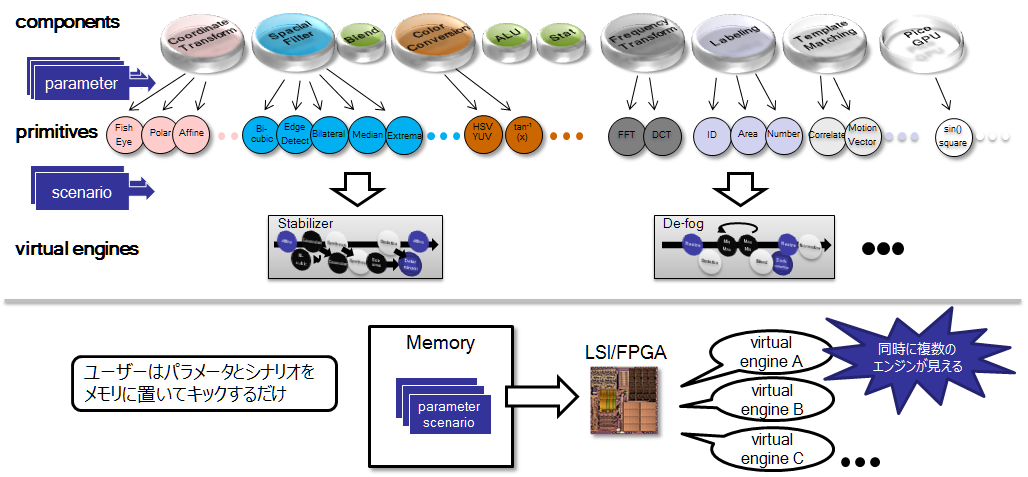

- 各部品にパラメータを与え、機能定義します。変換テーブル等細かい制御ができるため、きわめて高い柔軟性を持っています。

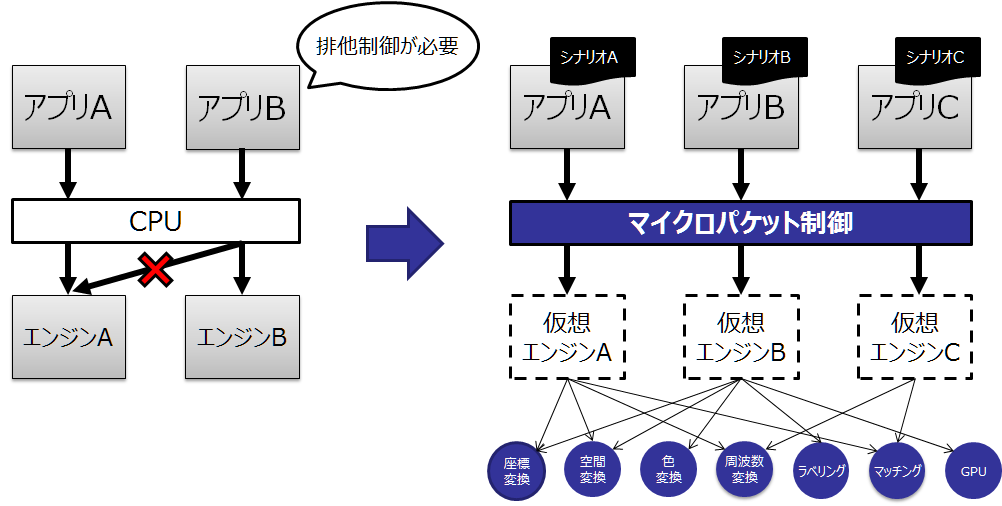

- アルゴリズムに従って、部品を組み合わせ(シナリオ記述)、仮想エンジン技術を使って実現すべきエンジンを定義します。

- 部品の一つGPUが、エンジン間をつなぐ演算処理を受け持ちます。ユーザーからは部品として見えます。

- 仮想エンジンは、1つのハードウェアエンジンとして処理します。起動のみの突き放し処理になり、CPU負荷を大幅に軽減します。

- 仮想エンジンは、アプリ(プロセス)毎に、同時に複製定義が可能です。ハードウェア資源の競合制御を解消します。

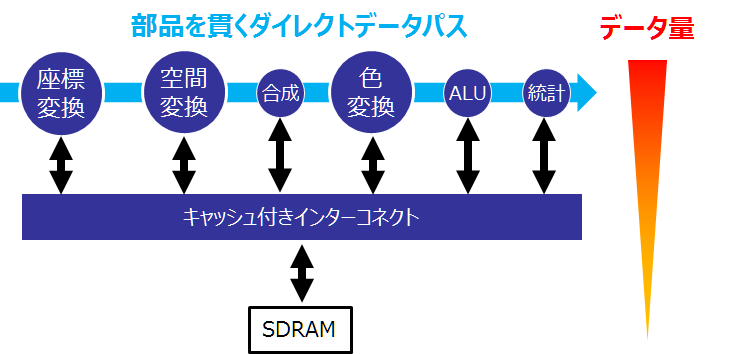

リアルタイム・低消費電力

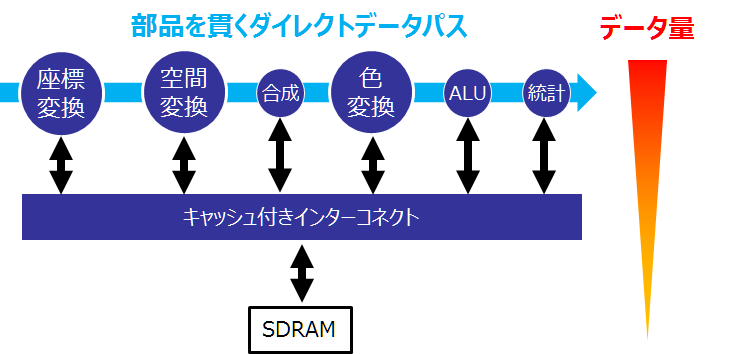

- 部品連結

IPEは、ソフトウェアを一切利用しない部品連結だけによるハードウェア処理を基本とするため、高いリアルタイム性と低消費電力性能を実現します。

- ハードウェア帯域の最大活用

複数シナリオの集約と各部品へのパケット分解(マイクロパケット制御)により、ハードウェア帯域を最大限に活用します。

加えて、パケット単位(画像であればライン)で処理を完結するので、高いリアルタイム性と低遅延を実現します。 - 低電力バスアーキテクチャ

使用順序の頻度が高い部品間をダイレクトに貫く専用のデータパスを持つことにより、外部メモリへのアクセスをミニマムに抑えます。また、パケットサイズが収まるキャッシュシステムによりさらに外部メモリへのアクセスを抑制します。これらの仕組みにより、ソフトウェア処理に対して1/10以下の低消費電力を実現します。

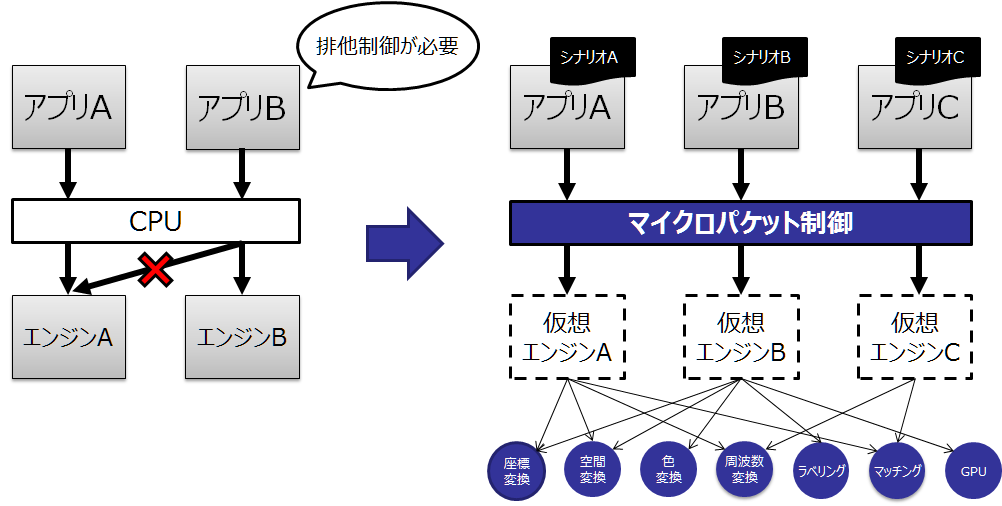

簡単制御

- 仮想エンジンは、アプリ(プロセス)毎に、同時複数定義可能です。

各アプリ(プロセス)からは、それぞれ独立したエンジンとして見えるため、ソフトウェアによるエンジン間のリソース調停は不要です。これにより、ソフトウェア設計はきわめて容易化します。

簡単プログラミング

- IPEのプログラミングは、以下2つの方法が利用可能です。これらの環境により、ソフトウェア開発工数を大幅に削減(一般的プログラミングに対して1/3以下)します。

汎用API(OpenVX)を活用したプログラミング(現在開発中)

OpenVXの主要関数を、IPEのアクセラレータにより高速実行します。

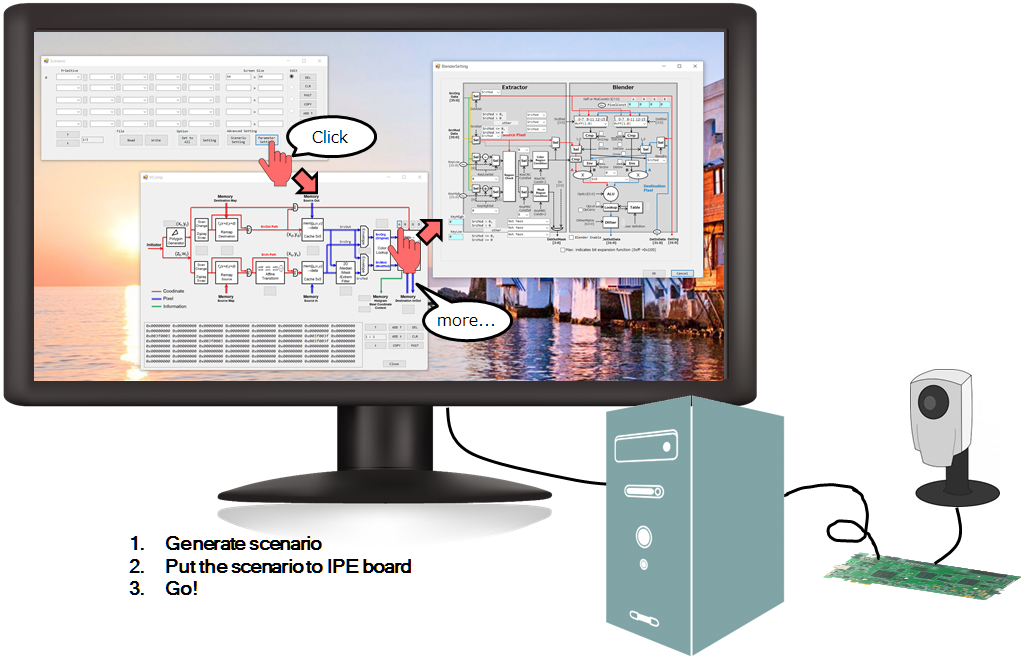

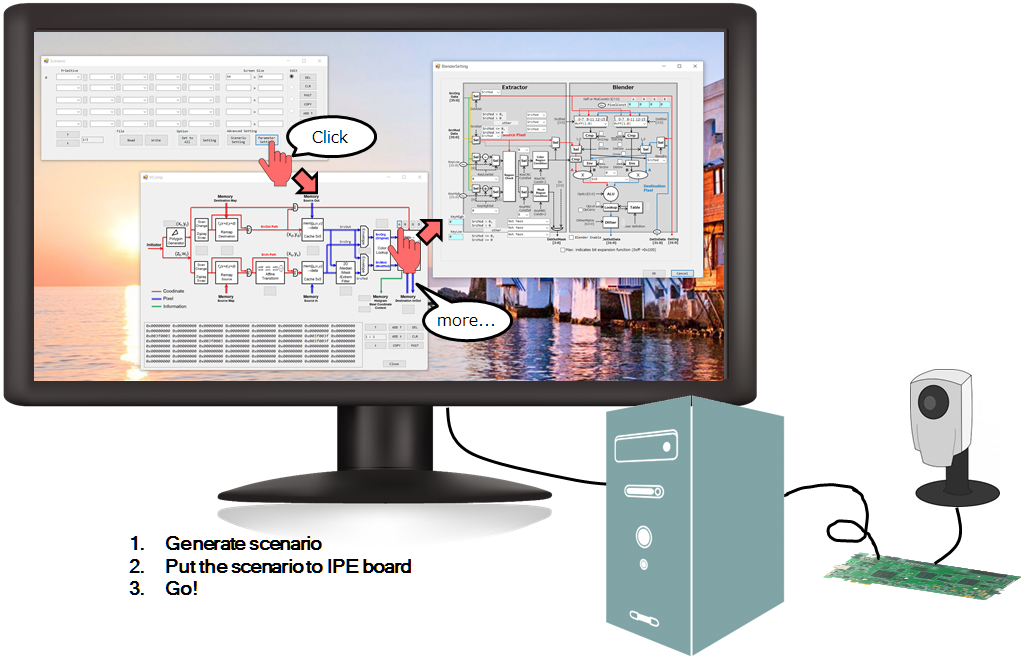

GUI記述(現在簡易版)

パラメータ設定および、部品の組み合わせ(シナリオ)をGUIにより記述する環境を提供します。

ハードウェア固有の特殊な知識を必要とせず、ハードウェアエンジンに最適な記述が可能です。

また、ハードウェアの性能を最大化させる最適化(部品結合)ツールも用意しています(現在開発中)。

具体的操作例はこちら